本文始于2025年4月,主要讲解DEF中相关语句含义。旨在让读者可以了解DEF中的相关语句基本的用法和基本含义。

创作声明:借AI协助。若内容有不完整之处或对本文有疑问的地方,请以lefdefref.pdf原文为准。

- 1. DEF 文件是什么?

- 2. DEF中的格式及语法说明

- 2.2 Bus Bit Characters

- 2.3 Component Mask Shift

- 2.4 Component

- 2.5 Design

- 2.6 Die Area

- 2.7 Divider Character

- 2.8 Extensions

- 2.9 Fills

- 2.10 GCell Grid

- 2.11 Groups

- 2.12 History

- 2.13 Nets

- 2.14 Nondefault Rules

- 2.15 Pins

- 2.16 Pin Properties

- 2.17 Property Definitions

- 2.18 Regions

- 2.19 Rows

- 2.20 Scan Chains

- 2.21 Slots

- 2.22 Special Nets

- 2.23 Styles

- 2.24 Technology

- 2.25 Tracks

- 2.26 Units

- 2.27 Version

- 2.28 Vias

1. DEF 文件是什么?

DEF(Design Exchange Format)文件是以 ASCII 格式 描述集成电路物理设计实现细节的,记录了电路设计在物理布局过程中的特定阶段的信息,它描述的是实际的设计。使用DEF文件可以在不同的设计系统间传递设计。它使用特定的语法规范来描述这些信息。

简单说:DEF 文件是芯片设计过程中,用于描述和传输设计物理信息的标准化文本格式。

DEF 文件的作用

DEF 文件起到在设计工具之间传递设计数据的桥梁作用,特别是在布局布线(place-and-route)工具中。具体包括以下几个方面:

- 逻辑设计数据:

- 网络连接(netlist)

- 分组信息(grouping)

- 物理约束(physical constraints)

- 物理设计数据:

- 器件的位置和方向(placement locations and orientations)

- 布线几何数据(routing geometry)

- 逻辑设计变化(用于backannotation)

2. DEF中的格式及语法说明

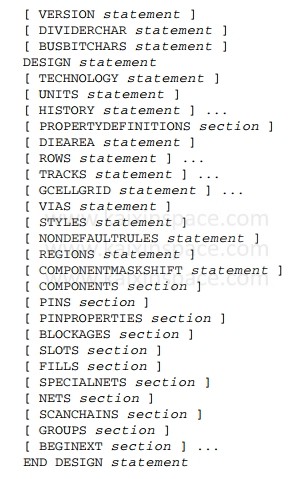

通常一个标准的DEF文件具有以下格式:

下面介绍各个字段的意义:

2.1 Blockages

语法:

BLOCKAGES <numBlockages> ;

[– LAYER <layerName>

[ + SLOTS | + FILLS]

[ + PUSHDOWN]

[ + EXCEPTPGNET]

[ + COMPONENT <compName>]

[ + SPACING <minSpacing> | + DESIGNRULEWIDTH <effectiveWidth>]

[ + MASK <maskNum>]

{RECT (<x1> <y1>) (<x2> <y2>)

| POLYGON (<x1> <y1>) (<x2> <y2>) (<x3> <y3>) … } … ;] …

[– PLACEMENT

[ + SOFT | + PARTIAL <maxDensity>]

[ + PUSHDOWN]

[ + COMPONENT <compName>]

{RECT (<x1> <y1>) (<x2> <y2>)} … ;] …

END BLOCKAGES 功能解释

BLOCKAGES 用于在 DEF 文件中定义放置和布线阻断区域(blockages),包括:

- routing blockages:阻止或限制该层的连线布线;

- placement blockages:阻止单元放置;

- fill/slot blockages:阻止金属填充或槽(slots)布置。

可定义全局区域性阻断,也可关联至特定实例(组件),随实例移动而移动citeturn0file0。

参数详细说明

| 参数 | 含义 |

|---|---|

numBlockages | 整数,指定本节中定义的阻断条目总数。 |

LAYER <layerName> | 指定在哪一层(通常为 routing 或 cut 层)建立阻断。切层阻断会阻止该区域内放置 via。 |

+ SLOTS / + FILLS | 分别表示在该层上阻止插槽(SLOTS)或金属填充(FILLS)。 |

+ PUSHDOWN | 表示该阻断是从顶层设计推下(push‑down)到子块的。 |

+ EXCEPTPGNET | 表示仅阻断信号网布线,不阻断电源/地线,可用于敏感区仅禁止信号穿过。 |

+ COMPONENT <compName> | 与某组件关联——只对该实例生效,实例若移动,阻断随之移动。 |

+ SPACING <minSpacing> | 覆盖该区域与其它同层形状的最小距离(单位:DEF 数据库单元),优先级高于所有层级默认间距规则。 |

+ DESIGNRULEWIDTH <effectiveWidth> | 将该区域“视作”指定宽度用于间距计算(与 SPACING 互斥)。20nm 及以下不允许使用。 |

+ MASK <maskNum> | 指定多重图案化掩膜编号(1、2 或 3),无该项则该区域“不着色”。 |

RECT (<x1> <y1>) (<x2> <y2>) | 用矩形定义阻断区域,两个点分别为左下/右上坐标(绝对坐标)。若关联组件,则仍为全局坐标。 |

POLYGON (<x1> <y1>) … | 至少三点,可定义矩形、多边形;边必须平行于 X/Y 轴或 45°。坐标可用 * 表示“与上一个点相同的 x/y 值”。 |

PLACEMENT | 定义放置阻断(而非布线阻断)。可进一步添加 + SOFT、+ PARTIAL、+ PUSHDOWN、+ COMPONENT。 |

+ SOFT | 初始放置阶段不使用此区域,但后续时序优化、时钟树插入可使用。 |

+ PARTIAL <maxDensity> | 初始放置时,此区域标准单元密度不超过 <maxDensity>%;后续缓冲插入可忽略此限制。 |

示例 1:多种阻断用法

BLOCKAGES 7 ;

# 1. 普通 routing 阻断

- LAYER metal1

RECT ( -300 -310 ) ( 320 330 )

RECT ( -150 -160 ) ( 170 180 ) ;

# 2. push‑down 类型 routing 阻断

- LAYER metal1 + PUSHDOWN

RECT ( -150 -160 ) ( 170 180 ) ;

# 3. 关联组件 i4 的 routing 阻断

- LAYER metal1 + COMPONENT |i4

RECT ( -150 -160 ) ( 170 180 ) ;

# 4. 浮动 placement 阻断

- PLACEMENT

RECT ( -150 -160 ) ( 170 180 ) ;

# 5. push‑down placement 阻断

- PLACEMENT + PUSHDOWN

RECT ( -150 -160 ) ( 170 180 ) ;

# 6. 关联组件 i3 的 placement 阻断

- PLACEMENT + COMPONENT |i3

RECT ( -150 -160 ) ( 170 180 ) ;

# 7. 阻断 fill 布局

- LAYER metal1 + FILLS

RECT ( -160 -170 ) ( 180 190 ) ;

END BLOCKAGES该段定义了 7 条阻断,涵盖 routing、placement、fill、多种修饰词组合。

示例 2:覆盖默认间距与指定等效宽度

BLOCKAGES 2 ;

# 最小间距 1000 数据库单元

- LAYER metal1 + SPACING 1000

RECT ( -300 -310 ) ( 320 300 )

POLYGON ( 0 0 ) ( * 100 ) ( 100 * ) ( 200 200 ) ( 200 0 ) ;

# 将此阻断“视作”宽度 1000 用于 DRC

- LAYER metal1 + DESIGNRULEWIDTH 1000

RECT ( -150 -160 ) ( 170 180 ) ;

END BLOCKAGES第一个阻断强制本区域与其它同层形状至少间隔 1000;第二个阻断在 DRC 视作 1000 宽。

2.2 Bus Bit Characters

语法

BUSBITCHARS "delimiterPair" ; 功能解释

- 指定用于在 DEF 名称与其它数据库(如 Verilog、OpenAccess)映射时标识总线位(bus bit)的成对定界符。

- 通过这一声明,读写 DEF 的工具就能识别诸如

DATA[3]之类的总线位标识,并在不同语法间正确转换。

参数详解

| 参数 | 含义 | 备注 |

|---|---|---|

delimiterPair | 由两个字符组成的字符串,第一个字符做“下标开始”,第二个做“下标结束” | 必须用双引号括起;例如 "[]", "()", "<>" |

- 缺省值:若未在 DEF 文件中指定,默认使用

"[]"。 - 转义:若定界符本身要在名称中作为普通字符出现,需在其前加反斜杠(

\)进行转义,否则将被误识别为总线下标。例如要表达名称A[3]X,在BUSBITCHARS "[]"情况下需写作A\[3\]X。

示例

1. 使用默认定界符 []

BUSBITCHARS "[]" ;ADDR[7]会被解析为信号ADDR的第 7 位。

2. 自定义为尖括号 < >

BUSBITCHARS "<>" ;- 现在需写

ADDR<7>来表示同一个总线位;如果要在名称里使用<,则要写\<。

2.3 Component Mask Shift

语法

COMPONENTMASKSHIFT <layer₁> [<layer₂> …] ; 功能解释

该语句为后续组件的 + MASKSHIFT 操作预先列出“可被 Mask 偏移”的层次顺序。

- 在多重图案化(double/triple patterning)工艺里,组件内不同金属或切层可被“着色”到不同掩膜(mask)上;

COMPONENTMASKSHIFT定义了某组件可以调整掩膜编号的层列表,从顶层金属到最底层金属依次排列;- 工具读到

+ MASKSHIFT时,会按此列表对各层做循环偏移(shift),以对齐或均衡各组件掩膜分布,提升布线密度。

参数详解

| 参数 | 含义 |

|---|---|

<layer₁> … | 一个或多个 LEF 中定义过的多掩膜层名称(routing 层或 cut 层),顺序必须“由高到低”。 |

示例

1. 声明可偏移层列表

# 指定该 DEF 文件内所有组件可对 M3→M2→VIA1→M1 层循环偏移掩膜

COMPONENTMASKSHIFT M3 M2 VIA1 M1 ;2. 对某实例应用偏移

COMPONENTS 1;

- i1/i2 AND2

+ MASKSHIFT 1102 # 对应层 M3→+1, M2→+1, VIA1→+0, M1→+2

;

END COMPONENTS其中 1102 的每位数字(从左到右)分别对应 M3、M2、VIA1、M1 的偏移量。掩膜编号超出最大值时循环回绕

这样,COMPONENTMASKSHIFT 与 + MASKSHIFT 配合使用,可灵活地对单个组件的多掩膜层进行色偏操作,提高工艺布线适应性。

2.4 Component

语法

COMPONENTS <numComps> ;

[- <compName> <modelName>

[+ EEQMASTER <macroName>]

[+ SOURCE {NETLIST | DIST | USER | TIMING}]

[+ {FIXED (<x> <y>) <orient>

| COVER (<x> <y>) <orient>

| PLACED (<x> <y>) <orient>

| UNPLACED}]

[+ MASKSHIFT <shiftLayerMasks>]

[+ HALO [SOFT] <left> <bottom> <right> <top>]

[+ ROUTEHALO <haloDist> <minLayer> <maxLayer>]

[+ WEIGHT <weight>]

[+ REGION <regionName>]

[+ PROPERTY {<propName> <propVal>} …]

;] …

END COMPONENTS 功能解释COMPONENTS 段定义了电路设计中的每个实例(组件)的型号、位置和多种属性,用于指导布局和布线工具如何处理这些实例:

- 固定/可动放置(

FIXED/PLACED/UNPLACED) - 电掩膜偏移(

+ MASKSHIFT) - 周边阻断(

+ HALO) - 路由边界(

+ ROUTEHALO) - 层次电等效(

+ EEQMASTER) - 分区/区域约束(

+ REGION) - 自定义属性(

+ PROPERTY)等。

参数详解

| 参数 | 含义 |

|---|---|

<numComps> | 整数,指定 COMPONENTS 段中组件条目总数。 |

<compName> <modelName> | 组件实例名与对应库中元件名(model),二者共同确定一个具体单元。 |

+ EEQMASTER <macroName> | 指定当前组件与另一个宏 macroName 在电气上等效,用于合并等效实例。 |

+ SOURCE {…} | 指示该实例放置/布线数据来源:网表(NETLIST)、分布式布局(DIST)、用户指定(USER)或时序驱动(TIMING)。 |

+ FIXED (x y) orient | 指定组件位置 (x,y) 且不能被自动工具移动;可通过交互命令手工移动。orient 为 N/S/E/W/FN…等方向。 |

+ COVER (x y) orient | 与 FIXED 类似,但表示此组件是“cover”宏的一部分,任何工具都不能移动。 |

+ PLACED (x y) orient | 指定初始放置位置,可被自动布局工具在后续步骤再优化;未放置则写 + UNPLACED。 |

+ MASKSHIFT <hexDigits> | 对照 COMPONENTMASKSHIFT 预定义的层列表,为实例的多掩膜层按位偏移掩膜编号;每位 hex 数对应一层的偏移值(2 掩膜层 0/1,3 掩膜层 0–5)citeturn1file3。 |

+ HALO [SOFT] l b r t | 在组件周围定义阻断边界:左/下/右/上分别扩展 l,b,r,t 单位。SOFT 表示仅在初始放置阶段生效,后续阶段可打破该边界。 |

+ ROUTEHALO d minL maxL | 在块边缘周围 d 单位范围内,针对从 minL 到 maxL 的路由层添加“路由走廊”,强制路由与块边缘垂直。 |

+ WEIGHT <weight> | 放置权重,非 0 则在自动布局时尽量靠近指定位置,但各非零值效果相同。 |

+ REGION <regionName> | 限制组件必须放置在 REGIONS 段定义的物理区域 regionName 内。 |

+ PROPERTY propName propVal | 为组件附加自定义属性(必须先在 PROPERTYDEFINITIONS 中定义),可用于脚本或后端工具做特殊处理。 |

2.5 Design

语法

DESIGN <designName> ; 功能解释DESIGN 语句用来在 DEF 文件中指定当前电路设计的名称。

- DEF 读入时,如果

<designName>与工具内部数据库已存在的设计名不一致,会发出警告; - 若发生冲突,DEF 中新指定的

<designName>会覆盖原有名称 。

参数详解

| 参数 | 含义 |

|---|---|

<designName> | 设计名标识符,用以标记本 DEF 文件对应的电路设计。• 由任意可打印 ASCII 字符组成(不含空格、制表符或换行)。• 最多 2 048 个字符。• 不用引号括起。 |

示例

# 为当前 DEF 文件定义设计名称为 DEMO4CHIP

DESIGN DEMO4CHIP ;

# 如果内部数据库原先名称不同,

# 工具将警告并改用“DEMO4CHIP”作为设计名2.6 Die Area

语法

DIEAREA (<x1> <y1>) (<x2> <y2>) [ (<x3> <y3>) … ] ; 功能解释DIEAREA 定义了整个芯片设计的 外形边界(封装/晶圆切割区域),可用于工具理解设计的可用空间和对齐坐标系。

- 若只给出两个点,则这两个点分别为矩形左下角和右上角;

- 若给出三个或以上点,则按顺序连成一个多边形,其边必须平行于 X 或 Y 轴(不允许 45° 斜边),并自动闭合最后一个点到第一个点。

- 所有坐标均为 DEF 数据库单位(通常对应微米缩放)。

参数详解

| 参数 | 含义 |

|---|---|

<xN> <yN> | 指定一个顶点坐标。• 两点时:第1点为左下角、第2点为右上角。• ≥3 点时:按给定顺序依次连线,并闭合。 |

| 单位 | 坐标值须为整数,以 DEF 文件中 UNITS 指定的数据库单位计量(常用 DISTANCE MICRONS 1000 等)。 |

示例

1. 矩形 Die Area

# 设计边界是 (0,0) 至 (10000,8000) 的矩形

DIEAREA ( 0 0 ) ( 10000 8000 ) ;2. 多边形 Die Area

# 定义一个“L”形区域:

DIEAREA

( 0 0 )

( 0 8000 )

( 4000 8000 )

( 4000 4000 )

( 10000 4000 )

( 10000 0 )

;2.7 Divider Character

语法

DIVIDERCHAR "<character>" ; 功能解释DIVIDERCHAR 声明用于在 DEF 名称与其它数据库(如 Verilog、OpenAccess)映射时,表示层次结构(hierarchy)分隔符的单个字符。例如在多层次设计中,用 TOP/SUB/INST 来标识实例路径时的 “/” 即为层级分隔符。

- 若 DEF 名称中需要包含该字符本身,则必须在字符前加反斜杠(

\)进行转义,否则会被误识为层级分隔符。 - 若未显式指定,工具会默认使用

"/"。

参数详解

| 参数 | 含义 |

|---|---|

<character> | 单个字符,用于分隔层次路径。• 必须以双引号括起,如 "/"、\. ":" 等。• 仅第一个字符有效,多余字符会报错。 |

示例

1. 使用默认层级分隔符 /

# 默认值,无需显式声明

# DIVIDERCHAR "/" ;- 名称

TOP/SUB/INST表示顶层模块TOP下的子模块SUB中的实例INST。

2. 自定义为句点 . 作为分隔符

DIVIDERCHAR "." ;- 现在需写

TOP.SUB.INST来表示相同层次路径;若要在名称里包含实际的 “.”,则写作A\.,例如A\.B。

3. 层级与总线下标混用

DIVIDERCHAR "/" ;

BUSBITCHARS "[]" ;

# 实例路径 A.B 的第 3 位总线

NET A/B[3] + USE SIGNAL ;- 读写时工具可正确识别

/为层次分隔符,[]为总线下标。

这样,DIVIDERCHAR 确保 DEF 文件在多层次环境中能统一且准确地解析实例路径。

2.8 Extensions

语法

BEGINEXT "tag"

extensionText>

ENDEXT 功能解释

BEGINEXT…ENDEXT定义了一段可由特定工具识别的扩展语法块,供那些不支持该扩展的工具安全忽略。- 可用于在 DEF 文件中嵌入用户自定义或尚未被标准 LEF/DEF 支持的新关键字、属性或注释。

参数详解

| 参数 | 含义 |

|---|---|

tag | 用双引号括起的字符串,标识此扩展块的名称或版本。 |

extensionText | 任意文本,可跨多行,直到遇到 ENDEXT 为止。通常包含:• 自定义关键字或语法摘录• 作者/工具信息• 时间戳、版本号等元数据 |

注意:

tag与ENDEXT必须严格匹配。- 扩展内容可以包含任何文本,但应避免干扰标准 DEF 语法(例如不要包含未闭合的分号)。

示例

# 定义一个名为 “1VSI Signature 1.0” 的扩展块

BEGINEXT "1VSI Signature 1.0"

CREATOR "Acme CAD Tools"

DATE "2025-04-17 10:23:45"

REVISION "r2.3.5"

ENDEXT在此示例中,后端或自定义脚本可以在解析 DEF 时检测到 1VSI Signature 1.0 扩展,并据此读取 CREATOR、DATE、REVISION 等自定义元数据;而不识别该扩展的通用 DEF 工具则会自动跳过该块,不影响对后续标准语句的解析。

2.9 Fills

语法

FILLS <numFills> ;

[– LAYER <layerName>

[ + MASK <maskNum>]

[ + OPC]

{RECT (<x1> <y1>) (<x2> <y2>)

| POLYGON (<x1> <y1>) (<x2> <y2>) (<x3> <y3>) … } … ;] …

[– VIA <viaName>

[ + MASK <maskMaskNum>]

[ + OPC]

(<x> <y>) … ;] …

END FILLS 功能解释FILLS 段用于在 DEF 文件中显式指定金属填充(fill)和via 补偿填充的几何形状:

- 金属填充:在指定层上增添矩形或多边形填充,以满足电镀/EM 漏电/DRC 限制;

- via 填充:在指定 via 类型处插入 via 形状,或对 via 进行多掩膜/OPC 标记。

这些填充通常由后端 DRC 或填充生成工具计算,DEF 中列出后可进行 mask 分色、OPC 处理和版图验证。

参数详解

| 参数 | 含义 |

|---|---|

<numFills> | 整数,表示随后出现的 - LAYER 与 - VIA 条目总数。注意:不是矩形/多边形的数量,而是“层”或“via”条目的数量。 |

LAYER <layerName> | 指定要在其上添加金属/多边形填充的层:通常为 routing 层(如 Metal1、Metal2),也可为 masterslice 或 implant 等层。 |

+ MASK <maskNum> | (可选)对该层填充使用的掩膜编号(patterning mask),整数。常见值 1、2 或 3。无该项时“无色”(uncolored)。 |

+ OPC | (可选)标记此填充图形需要在掩膜版生成时进行光学邻近修正(Optical Proximity Correction)。 |

RECT (x1 y1) (x2 y2) | 定义一个矩形填充,左下角 (x1,y1)、右上角 (x2,y2)。坐标以 DEF 数据库单位(通常映射到微米)给出。 |

POLYGON (x1 y1) … | 定义一个多边形填充,至少三个顶点;允许 45° 边。可用 * 重复前一点的同一坐标分量。 |

VIA <viaName> | (可选)插入 via 填充;<viaName> 必须先在 VIAS 段或 LEF 中定义。后续跟坐标列表指明放置位置。 |

+ MASK <maskMaskNum> | 与层填充的 MASK 语法相似,但 maskMaskNum 为三位十六进制值 <top><cut><bot>,用于多重 patterning 时分别对 via 上方金属、cut、下方金属上掩膜编号。 |

(<x> <y>) … | via 填充的坐标列表,每个点都放置一个相同类型的 via。 |

示例

1. 简单金属填充

FILLS 1 ;

- LAYER metal1

RECT ( 1000 2000 ) ( 1500 4000 )

RECT ( 2000 2000 ) ( 2500 4000 ) ;

END FILLS本例在 metal1 层上添加两块矩形填充,助力提高局部金属密度。

2. 多边形 & OPC 修正

FILLS 1 ;

- LAYER metal2 + OPC

POLYGON ( 100 100 ) ( 200 200 ) ( 300 200 ) ( 300 100 )

RECT ( 300 200 ) ( 350 400 ) ;

END FILLS在 metal2 层上生成一个多边形与一个矩形填充,并对它们进行 OPC 处理。

3. via 补偿 & 多掩膜

FILLS 2 ;

- VIA via1 + MASK 113

( 500 500 ) ( 800 800 ) ;

- VIA via2 + OPC

( 900 900 ) ;

END FILLSvia1在两点插入,通过MASK 113指定顶金属 & cut & 底金属 的掩膜编号(1/1/3);

via2在(900,900)加入 OPC 标记的 via;

2.10 GCell Grid

语法

GCELLGRID

{ X <start> DO <numCols+1> STEP <xSpace> } …

{ Y <start> DO <numRows+1> STEP <ySpace> ; } …

功能解释GCELLGRID 定义了标准单元设计中**分块网格(gcell grid)**的竖向与横向基准线(tracks)。

- 这些基准线将版图划分成若干“gcell”小矩形区域,每个 gcell 可用于路由分区与密度统计;

- 通常由路由器自动生成,设计者少手工编写;

- 横向与竖向可分别多次声明,形成统一或非统一网格。 citeturn4file0

参数详解

| 关键字 | 含义 |

|---|---|

X <start> | 定义第一条竖线(vertical track)的 X 坐标。 |

Y <start> | 定义第一条横线(horizontal track)的 Y 坐标。 |

DO <num+1> | 网格行/列数加一。若希望有 N 列(或行)gcell,就要画 N+1 条线。 |

STEP <space> | 相邻两条竖(横)线之间的间隔距离。 |

; | 每个 X… 或 Y… 子句以分号结束。 |

注意约束

- 最后一条基准线坐标必须小于(而非等于)对应的 gcell 边界坐标,否则会出现无归属的路由段。

- 声明的每个子句至少要定义一次 X… 和一次 Y…,以形成完整的矩形 gcell 网格。

示例

1. 均匀网格(所有 gcell 相同尺寸)

# 定义 100 列 × 200 行、gcell 大小 100×200:

GCELLGRID X 1000 DO 101 STEP 100 ;

GCELLGRID Y 1000 DO 201 STEP 200 ;- 竖线:从 X=1000 开始,101 条线,步长 100 → 划出 100 列宽度均为 100 的 gcell;

- 横线:从 Y=1000 开始,201 条线,步长 200 → 划出 200 行高为 200 的 gcell。 citeturn4file1

2. 非均匀网格(细分特定区域)

# 在原网格基础上,细分中间区域:

GCELLGRID X 3050 DO 61 STEP 50 ; # 中段细分:gcell 宽 50

GCELLGRID Y 5100 DO 51 STEP 100 ; # 中段细分:gcell 高 100- 在 X=3050 开始新增 61 条线、步长 50 → 对应 60 列宽 50 的子区域;

- 在 Y=5100 开始新增 51 条线、步长 100 → 对应 50 行高 100 的子区域;

- 结果网格整体呈非均匀分布,可在密集或关键路径区提升路由精度。 citeturn4file1

网格边界及归属规则

- gcell 边界:由最外层竖/横基准线围成;

- track 归属:若路由段落在 gcell 内,则归该 gcell;若恰好对齐在边界,只有贴左或贴下边界的段归当前 gcell,贴右或贴上边界的归下/右相邻 gcell。

2.11 Groups

语法

GROUPS <numGroups> ;

[– groupName [compNamePattern …]

[+ REGION regionName]

[+ PROPERTY {propName propVal} … ] …

;] …

END GROUPS 功能解释GROUPS 段用于将一组实例(组件)或逻辑对象打包到一个命名分组里,以便后续工具对整组应用统一约束或属性。例如,可将所有时钟网络实例分为一个“CLOCKS”组、将 I/O 单元分为“IO_PINS”组,从而在布局、布线或后端脚本中一次性操作整个组。

参数详解

| 参数 | 含义 |

|---|---|

<numGroups> | 整数,指定本节中定义的分组条目数。 |

<groupName> | 分组名称,用于后续引用。• 由可打印 ASCII 组成,不带引号。 |

<compNamePattern>… | 一个或多个组件名或带通配符(如 U*, CLK?)的名称模式,列出要包含在此组的实例。• 若为空,即空组,仅作占位。 |

+ REGION <regionName> | 将整个分组限制在先前 REGIONS 段定义的物理区域 <regionName> 内。 |

+ PROPERTY {…} | 为该分组附加用户自定义属性和值(需先在 PROPERTYDEFINITIONS 段定义属性名)。• 可指定多个 PROPERY 条目。 |

示例

# 定义两个分组:LOGIC 和 IO

GROUPS 2 ;

# 1) “LOGIC” 组,包含所有 U* (如 U1、U2…)组件,

# 并限制在 CORE 区域,且附加 AREA=“CORE_LOGIC”

- LOGIC U*

+ REGION CORE

+ PROPERTY AREA "CORE_LOGIC" ;

# 2) “IO_PINS” 组,包含所有以 IO 开头的实例,

# 并附加 AREA=“IO_BUFFER”

- IO_PINS IO*

+ PROPERTY AREA "IO_BUFFER" ;

END GROUPS

LOGIC组可用于对核心逻辑块统一设置时钟约束或阻断;IO_PINS组则可用于对 I/O 缓冲区施加独立的布线密度或延迟约束。

2.12 History

语法

HISTORY anyText ; 功能解释HISTORY 语句用于在 DEF 文件中记录设计更改的历史信息或注释。每一行 HISTORY 都代表一个记录条目,常用于标注版本、修改说明、工具或作者信息等。工具在解析时将这些行当作注释,不影响布局布线过程,也不会合并为同一条——每行独立。

参数详解

| 参数 | 含义 |

|---|---|

<anyText> | 任意文本(除分号 ; 外的所有字符),作为该历史条目的内容。• 不可跨行:遇到分号即终止本条目,回车不视为结束。• 可多次使用,每条记录一行。 |

示例

# 先前的 FLOORPLAN 由脚本 floorplan_v1 生成

HISTORY Floorplan generated by floorplan_v1 script on 2025-04-10 ;

# 后续由 Alice 手工调整 ROWS 参数

HISTORY Rows adjusted by Alice: row pitch changed to 0.8 μm ;

# 用 Cadence ICC2 做最后验证

HISTORY Final DRC run with Cadence ICC2, no violations found ;- 每条

HISTORY行都会被工具保留为单独的注释记录; - 可在文件中任何位置(但通常紧跟在

UNITS或DESIGN之后)添加多条,用于追踪设计演进。

2.13 Nets

语法

NETS <numNets> ;

[– { <netName>

[ ( { <compName> <pinName> | PIN <pinName> } [+ SYNTHESIZED] ) … ]

| MUSTJOIN ( <compName> <pinName> )

}

[ + SHIELDNET <shieldNetName> ] …

[ + VPIN <vpinName> [ LAYER <layerName> ] <x> <y>

[ PLACED <x> <y> <orient>

| FIXED <x> <y> <orient>

| COVER <x> <y> <orient>

]

] …

[ + SUBNET <subnetName>

[ ( { <compName> <pinName> | PIN <pinName> | VPIN <vpinName> } ) … ]

[ NONDEFAULTRULE <ruleName> ]

[ <regularWiring> ] …

] …

[ + XTALK <class> ]

[ + NONDEFAULTRULE <ruleName> ]

[ <regularWiring> ] …

[ + SOURCE { DIST | NETLIST | TEST | TIMING | USER } ]

[ + FIXEDBUMP ]

[ + FREQUENCY <frequency> ]

[ + ORIGINAL <oldNetName> ]

[ + USE { ANALOG | CLOCK | GROUND | POWER | RESET | SCAN | SIGNAL | TIEOFF } ]

[ + PATTERN { BALANCED | STEINER | TRUNK | WIREDLOGIC } ]

[ + ESTCAP <wireCapacitance> ]

[ + WEIGHT <weight> ]

[ + PROPERTY { <propName> <propVal> } … ]

;] …

END NETS 功能解释

NETS 节定义设计中所有电气连线(nets),包括:

- 连接关系:用实例名+引脚或顶级 I/O

PIN绑定到网络; - 特殊连接:

MUSTJOIN强制将多个引脚短接为同一网络; - 屏蔽/耦合:

SHIELDNET指定为屏蔽网线;XTALK定义串扰分级; - 虚拟管脚(VPIN):用于 IO pad 或功率网的 pad 定位;

- 子网(SUBNET):在一条大网内定义局部子网,可应用不同布线或 DRC 规则;

- 布线风格:

regularWiring(如ROUTED metal1 (x1 y1) …)指明布线路径; - 约束与属性:

SOURCE、USE、NONDEFAULTRULE、ESTCAP、WEIGHT、自定义PROPERTY等。

参数详解

| 参数/关键字 | 必需 | 类型 & 范围 | 详细解释 |

|---|---|---|---|

<netName> | 是 | 字符串(≤2048 字符) | 网络的唯一标识。可含层级和总线下标(受 DIVIDERCHAR、BUSBITCHARS 影响)。示例: CLK, DATA[7], TOP/SUB/NET1。 |

( … ) 列表 | 是 | 列表,每项:<compName> <pinName> 或 PIN <pinName> | 指明此网络连接的引脚: – 实例引脚: U1 A、U2 Z;– 顶级 I/O: PIN RESET。可加 + SYNTHESIZED 标记综合工具自动插入的端口。 |

MUSTJOIN ( … ) | 否 | 单一项:<compName> <pinName> | 强制将该引脚与本网络内所有其它成员短接,无论常规连线如何;常用于电源环路、测试点、自动插针等。 |

+ SHIELDNET <shieldNet> | 否 | 字符串,对应另一 netName | 指定一个屏蔽网。路由器会维持本网与屏蔽网之间的最小间距,或在二者间插入金属守护线(shielder),提升敏感信号抗扰度。 |

+ VPIN | 否 | 结构:VPIN <vpinName> [LAYER <layer>] x y [PLACED…] | 虚拟管脚,用于 PAD、IO Pad 或功率网边界: – <vpinName>:自定义管脚名;– LAYER:所属层(如 metal1),默认为网络首层;– x y:绝对坐标;– PLACED/FIXED/COVER:定位与可动性约束;如 + VPIN VP1 LAYER metal2 1000 2000 PLACED 1000 2000 N。 |

+ SUBNET <name> | 否 | 子网名(字符串) | 在主网内部再细分一个子网,可单独应用布线与 DRC 规则。 – 接下来的 (...) 列出该子网成员(与主网相同语法);– 可添加 NONDEFAULTRULE、regularWiring(如 ROUTED metal3 (…);)。示例: + SUBNET CORE_CLK ( U1 CLK U2 CLK ) NONDEFAULTRULE slowRoute ROUTED metal4 (0 0)(100 0); |

regularWiring | 否 | 关键字 ROUTED 或 FIXEDPATH…… | 指定网络的布线路径: – ROUTED <layer> (x1 y1) (x2 y2) … ;– FIXEDPATH 表示不可修改的布线段。此段必须以分号结尾。 |

+ XTALK <class> | 否 | 字符串或整数 | 将此网归入某个串扰类别,比如 + XTALK 2。工具可针对同类网络做串扰分析或插入额外屏蔽。 |

+ NONDEFAULTRULE <r> | 否 | 字符串(对应 LEF 中 NONDEFAULTRULE) | 在该网布线时,使用自定义间距/最小宽度/最小切割数等规则。常见于关键网络或高密度区域。 |

+ SOURCE {…} | 否 | 枚举:NETLIST/DIST/TEST/TIMING/USER | 描述该网数据来源: – NETLIST:来自逻辑网表;– DIST:布图区段自动分配;– TEST:测试针脚;– TIMING:时序驱动;– USER:手工指定。 |

+ FIXEDBUMP | 否 | 关键字 | 标记此网络为 Bump/Pad 网络,走线与 via 位置不可被自动优化工具随意移动。 |

+ FREQUENCY <f> | 否 | 浮点数 / 整数(MHz) | 对时钟或高频网络标注工作频率,用于信号完整性(SI)和热分析。 |

+ ORIGINAL <oldNet> | 否 | 字符串(网络名) | 指明本网络是由旧网络 <oldNet> 重命名或拆分而来,便于 Back‑annotation 追溯。 |

+ USE {…} | 否 | 枚举:ANALOG/CLOCK/GROUND/POWER/RESET/SCAN/SIGNAL/TIEOFF | 描述网络的用途。 – POWER/GROUND:电源;– CLOCK:时钟;– SIGNAL:普通信号;– 其余用于扫描链、复位、模拟等特殊网络。 |

+ PATTERN {…} | 否 | 枚举:BALANCED/STEINER/TRUNK/WIREDLOGIC | 指定主干–树型–平衡–有线逻辑等布线拓扑偏好,常用于时钟树或高性能信号。 |

+ ESTCAP <cap> | 否 | 浮点数(pF 或 DEF 单位) | 对网络进行电容估算,帮助时序和功耗分析。 |

+ WEIGHT <w> | 否 | 整数 / 浮点数 | 布线器分配资源的优先级权重,数值越大优先度越高。 |

+ PROPERTY {…} | 否 | 多项:<propName> <propVal> | 自定义属性键值对,必须先在 PROPERTYDEFINITIONS 中定义。可用于后端脚本或 DFT 流程。 |

示例

NETS 2 ;

# 1) 时钟网络:Steiner 布线、100MHz

- CLK

(U1 CLK) + SYNTHESIZED

(U2 CLK) + SYNTHESIZED

+ USE CLOCK

+ SOURCE TIMING

+ FREQUENCY 100

+ PATTERN STEINER

+ ROUTED metal3 ( 0 0 ) ( 500 0 ) ( 500 200 ) ( 1000 200 ) ;

# 2) 电源网络,含子网与屏蔽

- VDD

(U1 VDD)

+ USE POWER

+ SUBNET VDD_CORE ( U2 VDD )

NONDEFAULTRULE highDensity

ROUTED metal2 ( 0 0 ) ( 0 1000 ) ;

+ SHIELDNET GND

+ ROUTED metal1 ( 0 0 ) ( 1000 0 ) ;

END NETSCLK网络自动综合插入,应用时序驱动布线,100 MHz,Steiner 拓扑。VDD为电源网,在U1、U2处形成两个子网,核心子网采用highDensity布线规则,并与地线GND屏蔽。

2.14 Nondefault Rules

语法

NONDEFAULTRULES <numRules> ;

– <ruleName>

[ + HARDSPACING ]

{ + LAYER <layerName>

WIDTH <minWidth>

[ DIAGWIDTH <diagWidth> ]

[ SPACING <minSpacing> ]

[ WIREEXT <wireExtension> ]

END <layerName>

} …

[ + VIA <viaName> ] …

[ + VIARULE <viaRuleName> ] …

[ + MINCUTS <cutLayerName> <numCuts> ] …

[ + PROPERTY { <propName> <propVal> } … ] …

; …

END NONDEFAULTRULES 功能解释

NONDEFAULTRULES 段用于在 DEF 中声明非缺省(custom)布线规则,这些规则可在 NETS/SUBNET 节中通过 + NONDEFAULTRULE <ruleName> 显式指定,以覆盖 LEF 中的默认宽度、间距、via 选择等设置。常用于:

- 关键路径信号(加宽、加密间距);

- 模拟/射频网络(专用 via、硬间距);

- 高频或大电流网络(最小切数);

- 与网表或后端工具共享特殊属性。

参数详解

| 参数 | 类型 / 取值范围 | 默认值 | 含义 |

|---|---|---|---|

<numRules> | 正整数 | — | 本段落中定义的规则条目总数。 |

<ruleName> | 字符串 | — | 规则标识符,用于 + NONDEFAULTRULE <ruleName> 中引用。保留名 DEFAULT 可用来显式覆盖默认规则。 |

+ HARDSPACING | 关键字 | 软间距(soft) | 将本规则中所有 SPACING 要求视作“硬违规”,路由时不可违背;默认为“软违规”可在拥塞时高成本违背。 |

+ LAYER … END <layer> | 块状配置: • WIDTH(Float,μm)• [DIAGWIDTH](Float,μm)• [SPACING](Float,μm)• [WIREEXT](Float,μm) | — / 0 / LEF / WIDTH/2 | 分层路由规则: • WIDTH:最小线宽;• DIAGWIDTH:45° 段宽;0 表示禁用;• SPACING:额外最小间距;• WIREEXT:via 处延伸量。 |

+ VIA <viaName> | 字符串,LEF/DEF 中已定义的 via 名 | — | 指定可供该规则使用的 via 类型,可列多项,路由器择优。 |

+ VIARULE <ruleName> | 字符串,LEF 中 VIARULE GENERATE 名 | 默认 GENERATE DEFAULT | 使用自定义 via 生成规则,覆盖默认 via 生成。 |

+ MINCUTS <cut> <n> | <cut>=切层名,<n>=正整数 | 1 | 针对指定切层,要求 至少生成 n 个切孔,常用于大电流或可靠性敏感场合。 |

+ PROPERTY {…} | 键值对列表,propName=字符串,propVal=数值或字符串 | — | 附加自定义属性(需先在 PROPERTYDEFINITIONS 中声明),用于后端脚本或 DFT 流程。 |

示例

1. 简单加宽规则

NONDEFAULTRULES 1 ;

- wide1_5x

+ LAYER metal1

WIDTH 1.5 ; # 将 metal1 线宽设为 1.5μm(默认 1.0μm)

END metal1

+ LAYER metal2

WIDTH 1.5 ;

END metal2

+ LAYER metal3

WIDTH 1.5 ;

END metal3

;

END NONDEFAULTRULES该规则定义名为 wide1_5x 的三层加宽布线,间距与 via 继承默认citeturn5file0。

2. 最少双切 VIA 规则

NONDEFAULTRULES 1 ;

- wide3x

+ LAYER metal1

WIDTH 3.0 ;

END metal1

+ LAYER metal2

WIDTH 3.0 ;

END metal2

+ LAYER metal3

WIDTH 3.0 ;

END metal3

+ MINCUTS cut12 2 ; # cut12 至少 2 切孔

+ MINCUTS cut23 2 ;

;

END NONDEFAULTRULESwide3x 除加宽外,强制 key vias 生成 ≥2 切孔citeturn5file0。

3. 模拟网络专用规则

NONDEFAULTRULES 1 ;

- analog_rule

+ HARDSPACING ; # 额外间距作为硬性违规

+ LAYER metal1

WIDTH 1.5

SPACING 3.0 # 强制 3.0μm 额外间距

END metal1

+ LAYER metal2

WIDTH 1.5

SPACING 3.0

END metal2

+ VIA via12_fixed_analog_via ; # 使用专用固定 via

+ VIARULE via_23_fixed_analog_via # 或通过 VIARULE 指定

;

END NONDEFAULTRULESanalog_rule 在三层均施加强制间距,并指定专用 via,不继承默认 via 规则citeturn5file0。

通过在 NETS 或 SUBNET 中使用

+ NONDEFAULTRULE <ruleName>即可对指定网络应用上述自定义布线规则,灵活满足关键路径、模拟或电源网络的特殊需求。

2.15 Pins

语法

PINS <numPins> ;

– <pinName> + NET <netName>

[ + SPECIAL ]

[ + DIRECTION {INPUT | OUTPUT | INOUT | FEEDTHRU} ]

[ + NETEXPR "<netExprPropName> <defaultNetName>" ]

[ + SUPPLYSENSITIVITY <powerPinName> ]

[ + GROUNDSENSITIVITY <groundPinName> ]

[ + USE {SIGNAL | POWER | GROUND | CLOCK | TIEOFF | ANALOG | SCAN | RESET} ]

[ + ANTENNAPINPARTIALMETALAREA <value> [ LAYER <layerName> ] ]

[ + ANTENNAPINPARTIALMETALSIDEAREA <value> [ LAYER <layerName> ] ]

[ + ANTENNAPINPARTIALCUTAREA <value> [ LAYER <layerName> ] ]

[ + ANTENNAPINDIFFAREA <value> [ LAYER <layerName> ] ]

[ + ANTENNAMODEL {OXIDE1 | OXIDE2 | OXIDE3 | OXIDE4} ]

[ + ANTENNAPINGATEAREA <value> [ LAYER <layerName> ] ]

[ + ANTENNAPINMAXAREACAR <value> LAYER <layerName> ]

[ + ANTENNAPINMAXSIDEAREACAR <value> LAYER <layerName> ]

[ + ANTENNAPINMAXCUTCAR <value> LAYER <layerName> ]

[

+ PORT

( + LAYER <layerName>

[ MASK <maskNum> ]

[ SPACING <minSpacing> | DESIGNRULEWIDTH <effWidth> ]

<x1> <y1> [ ( <x2> <y2> ) … ]

| + POLYGON <layerName>

[ MASK <maskNum> ]

[ SPACING <minSpacing> | DESIGNRULEWIDTH <effWidth> ]

<x1> <y1> <x2> <y2> <x3> …

| + VIA <viaName> [ MASK <viaMaskNum> ] <x> <y>

) …

[ + COVER <x> <y> <orient>

| + FIXED <x> <y> <orient>

| + PLACED <x> <y> <orient> ]

] …

; …

END PINS 功能解释PINS 段用于定义设计块(block)或芯片级别的I/O 引脚,将外部引脚名映射到内部网 NET,并给出物理几何、方向、属性和工艺相关信息。可细分为:

- 逻辑连接:

+ NET、+ DIRECTION、+ USE、+ NETEXPR、敏感度; - 物理几何:通过一个或多个

+ PORT子段,列出在各层的LAYER矩形/多边形/VIA位置; - 放置属性:

+ PLACED/+ FIXED/+ COVER指示引脚在版图中的定位与可动性; - 特殊标志:

+ SPECIAL(特殊引脚)、NEW SENSITIVITY(电源/地)、+ USE(信号用途); - 工艺/电气约束:一系列

ANTENNA*语句用于工艺天线规则、SPACING/DESIGNRULEWIDTH针对引脚形状间距。

参数详解

| 参数 | 类型 / 范围 | 默认 | 说明 |

|---|---|---|---|

<numPins> | 正整数 | — | 本段定义的引脚总数。 |

<pinName> | 字符串 | — | 外部引脚名,可含层级与总线位,受 DIVIDERCHAR/BUSBITCHARS 影响。 |

+ NET <netName> | 字符串 | — | 指定此引脚关联的内部网络名。 |

+ SPECIAL | 关键字 | 否 | 标记为“特殊引脚”,普通路由器不通,用于 power‑mesh、高速总线等由专用路由器处理。 |

+ DIRECTION {…} | 枚举:INPUT/OUTPUT/INOUT/FEEDTHRU | — | 引脚方向,用于时序、DFT 和 netlist 映射。 |

+ NETEXPR "<expr> <default>" | 字符串 | — | 通过 <expr> 在网表中查找网名,找不到则用 <default>。仅需在同一网络的一个引脚上声明。 |

+ SUPPLYSENSITIVITY <pin> | 字符串(+ USE POWER pinName) | — | 若该引脚连到 tie‑high(1’b1),应连至 pinName 所在电源网;仅当有多个 power 引脚时生效。 |

+ GROUNDSENSITIVITY <pin> | 字符串(+ USE GROUND pinName) | — | 同理,用于 1’b0 自动连地。 |

+ USE {…} | 枚举 | SIGNAL | 引脚用途:POWER/GROUND/CLOCK/ANALOG/SCAN/RESET/TIEOFF/SIGNAL,辅助工具优化布局布线和 SI 分析。 |

+ ANTENNAPINPARTIALMETALAREA… | Float (μm²) + [ LAYER ] | — | 指定连至此引脚的金属面积(不含侧面)用于天线比检查;可对各层分别设置。 |

+ ANTENNAPINPARTIALMETALSIDEAREA… | Float (μm²) + [ LAYER ] | — | 指定金属侧面面积,用于天线侧面比。 |

+ ANTENNAPINPARTIALCUTAREA… | Float (μm²) + [ LAYER ] | — | 指定切层(via cut)面积,用于天线切层比。 |

+ ANTENNAPINDIFFAREA… | Float (μm²) + [ LAYER ] | — | 指定扩散(diode)面积,用于工艺天线扩散比。 |

+ ANTENNAMODEL {OXIDE1…} | 枚举 | OXIDE1 | 天线模型标签,作用于后续 ANTENNAPINMAX*CAR。 |

+ ANTENNAPINGATEAREA… | Float (μm²) + [ LAYER ] | — | 指定栅极面积,用于天线栅加扩散比。 |

+ ANTENNAPINMAXAREACAR… | Float + LAYER | — | 指定最大累积金属‑切层比 (CAR),与 ANTENNAMODEL 共同使用。 |

+ ANTENNAPINMAXSIDEAREACAR… | Float + LAYER | — | 最大累积侧面天线比。 |

+ ANTENNAPINMAXCUTCAR… | Float + LAYER | — | 最大累积切层比。 |

+ PORT 子句 | 见下表 | — | 描述该引脚在物理版图中的一个“端口”位置,可有多个端口,适用于 power‑pad 多侧取电或双侧 I/O。 |

| 放置子句 | + PLACED/+ FIXED/+ COVER | — | 指示该端口的位置 (x,y) 和方向:– PLACED:可被工具再次优化;– FIXED:仅可交互式移动;– COVER:工具绝不可移动。orient 为 N/S/E/W/FN/FS/FW/FE citeturn6file2。 |

端口层几何 (+ LAYER) | LAYER <layer> (x1 y1) (x2 y2) | — | 用矩形定义该端口在 <layer> 上的形状;后可加 MASK、SPACING 或 DESIGNRULEWIDTH 覆盖。 |

多边形几何 (+ POLYGON) | POLYGON <layer> (x1 y1) (x2 y2) … | — | 至少三点,允许 45° 边。 |

Via 几何 (+ VIA) | VIA <viaName> [MASK <maskNum>] (x y) | — | 在该端口插入 named via,并可指定多重图案化掩膜。 |

示例

PINS 2 ;

- BUSA[0] + NET BUSA[0] + DIRECTION INPUT + USE SIGNAL

+ LAYER M2 ( -30 0 ) ( 30 150 )

+ VIA via12 ( 0 25 )

+ PLACED ( -2100 -5000 ) N ;

- VDD + NET VDD + DIRECTION INOUT + USE POWER + SPECIAL

+ PORT

+ LAYER M2 ( -25 0 ) ( 25 50 )

+ PLACED ( 0 2500 ) S

+ PORT

+ LAYER M1 ( -25 0 ) ( 25 50 )

+ PLACED ( -2500 0 ) E

+ PORT

+ LAYER M1 ( -25 0 ) ( 25 50 )

+ PLACED ( 2500 0 ) W ;

END PINS- BUSA[0]:信号引脚,

M2矩形端口加 via12,通过PLACED定位于下边中点citeturn6file2。 - VDD:电源引脚,标记

SPECIAL,有三个物理端口(top/mid/bottom)分布在三侧,用专用路由器连接。

2.16 Pin Properties

语法

PINPROPERTIES <numPins> ;

[– { <compName> <pinName> | PIN <pinName> }

[ + PROPERTY { <propName> <propVal> } … ]

; ] …

END PINPROPERTIES 功能解释PINPROPERTIES 段用来为已有的组件引脚或顶级 I/O 引脚(定义于 PINS 节或 COMPONENTS 节)附加自定义属性值,这些属性必须事先在 PROPERTYDEFINITIONS 中声明。属性往往用于时序、功耗、DFT 或脚本驱动流程中的特殊标记和约束。

参数详解

| 参数 | 类型 / 取值 | 必需 | 含义 |

|---|---|---|---|

<numPins> | 正整数 | 是 | 本段中条目数,与后续 – 行数相同。 |

<compName> <pinName> | 两个字符串 | 是 | 组件实例引脚:compName 为实例名,pinName 为该实例的引脚名。 |

PIN <pinName> | 关键字 + 字符串 | 是 | 顶级 I/O 引脚:直接用 PIN 表示,不归属于任何组件实例。 |

+ PROPERTY {…} | 键值对列表 | 否 | 指向在 PROPERTYDEFINITIONS 中声明的属性,并赋予该引脚具体值。可指定多组。– <propName>:属性名;– <propVal>:数值或用双引号括起的字符串。 |

示例

假设在 PROPERTYDEFINITIONS 中已定义:

PROPERTYDEFINITIONS

PIN CLOCK STRING ;

END PROPERTYDEFINITIONSPINPROPERTIES 3 ;

# 1. 为 CORE/g76 上的 CKA 引脚标记时钟触发类型

- CORE/g76 CKA

+ PROPERTY CLOCK "FALLING" ;

# 2. 为 comp1 实例的 A 引脚排除时钟插入

- comp1 A

+ PROPERTY CLOCK "EXCLUDED" ;

# 3. 为 rp/regB 实例的 clk 引脚指定时钟插入方式

- rp/regB clk

+ PROPERTY CLOCK "INSERTION" ;

END PINPROPERTIES- 第一行声明 3 个引脚属性条目。

- 每条

-开头的行指定目标引脚及其CLOCK属性值。 - 工具在后端可据此区分不同引脚的时钟偏好。

2.17 Property Definitions

语法

PROPERTYDEFINITIONS

[<objectType> <propName> <propType>

[RANGE <min> <max>]

[<value> | "<stringValue>"]

;] …

END PROPERTYDEFINITIONS 功能解释PROPERTYDEFINITIONS 段用于集中声明后续可在 DEF 文件各节(如 PINS、NETS、REGIONS、ROWS 等)中使用的自定义属性

- 指定作用对象(

objectType),确保属性只能附加到合法的 DEF 对象上; - 定义数据类型(

INTEGER、REAL、STRING),并可选地限定数值范围; - 对于顶层或库级属性,还可提供一个默认值。

这保证了 DEF 中属性引用的一致性与可验证性citeturn7file0。

参数详解

| 参数 | 必需 | 类型 / 取值范围 | 默认 | 说明 |

|---|---|---|---|---|

objectType | 是 | 枚举:COMPONENT、COMPONENTPIN、DESIGN、GROUP、NET、NONDEFAULTRULE、PIN、REGION、ROW、SPECIALNET、VIA、VIARULE | — | 声明该属性可应用的 DEF 对象类型。 |

propName | 是 | 字符串(≤2048 字符) | — | 属性标识,用于 + PROPERTY propName propVal 引用。 |

propType | 是 | 枚举:INTEGER / REAL / STRING | — | 属性值的数据类型。– INTEGER:整数;– REAL:浮点;– STRING:文本(引用时用双引号)。 citeturn7file1 |

RANGE <min> <max> | 否 | 数值,针对 INTEGER 或 REAL | 全域 | 限定数值型属性的最小/最大值,赋值时需满足 min ≤ value ≤ max,否则解析报错。 |

<value> | 否 | 对应 INTEGER 或 REAL | — | 在 DESIGN 等顶层对象中,定义属性的默认数值。 |

"<stringValue>" | 否 | 双引号内任意文本 | — | 在 DESIGN 或 LIBRARY 等顶层对象中,定义属性的默认文本。 |

示例

PROPERTYDEFINITIONS

# 设计级属性:版本号(整数,范围 1–10,默认 3)

DESIGN versionNum INTEGER RANGE 1 10 3 ;

# 设计级属性:标题(字符串,无默认值)

DESIGN title STRING ;

# VIA 级属性:计数(整数,范围 1–100)

VIA viaCount INTEGER RANGE 1 100 ;

# MACRO 级属性:权重(浮点,范围 1.0–50.0)

MACRO weight REAL RANGE 1.0 50.0 ;

# MACRO 级属性:类型(字符串)

MACRO type STRING ;

END PROPERTYDEFINITIONSversionNum可在DESIGN节通过+ PROPERTY versionNum 5赋值;viaCount在VIA节可用+ PROPERTY viaCount 3,且必须介于 1–100;type在MACRO节可用+ PROPERTY type "CORE"赋文本值。

2.18 Regions

语法

REGIONS <numRegions> ;

– <regionName> (<x1> <y1>) (<x2> <y2>) …

[ + TYPE {FENCE | GUIDE} ]

[ + PROPERTY {<propName> <propVal>} … ]

; …

END REGIONS 功能解释REGIONS 用于在 DEF 文件中定义一个或多个物理区域(region),这些区域可用于

- 限制放置:将

COMPONENTS或GROUPS关联到特定区域; - 引导布局:通过

TYPE GUIDE为工具提供放置偏好; - 元数据标注:用自定义属性对区域进行分级或打标签,以辅助后端脚本或约束生成。

参数详解

| 参数 | 类型 / 取值 | 默认 | 说明 |

|---|---|---|---|

<numRegions> | 正整数 | — | 本节定义的区域总数,与后续以 – 开头的条目数一致。 |

<regionName> | 字符串 | — | 区域标识符,用于 COMPONENTS/GROUPS 中的 + REGION <regionName> 表达式。 |

(<x> <y>) … | 一对或多对整数坐标 | — | 按次序列出矩形区域的顶点坐标;– 两点时:第 1 点为左下、 第 2 点为右上;– ≥3 点时:依序闭合多边形(边仅平行于 X/Y 轴)。 |

| `+ TYPE {FENCE | GUIDE}` | 枚举 | FENCE |

+ PROPERTY {…} | 一组键值对 | — | 引用先前在 PROPERTYDEFINITIONS 中声明的属性,并为本区域赋值,常用于层级化标记、批量脚本处理或自定义验证。 |

示例

# 定义两个区域:CORE_AREA、IO_AREA

REGIONS 2 ;

# 1) 硬性围栏区 CORE_AREA:矩形 (0,0)-(10000,8000)

- CORE_AREA ( 0 0 ) ( 10000 8000 )

+ TYPE FENCE

+ PROPERTY REGIONORDER 1

+ PROPERTY PURPOSE "CORE_LOGIC"

;

# 2) 软性向导区 IO_AREA:L 形

- IO_AREA

( 0 8000 ) ( 2000 10000 )

( 0 12000 ) ( 10000 20000 )

( 8000 8000 ) ( 10000 12000 )

+ TYPE GUIDE

+ PROPERTY REGIONORDER 2

+ PROPERTY PURPOSE "IO_BUFFER"

;

END REGIONS- CORE_AREA:用

FENCE强制所有+ REGION CORE_AREA的组件只能放置在(0,0)到(10000,8000)内。 - IO_AREA:用

GUIDE提示工具“最好”将 I/O 缓冲区放入此 L 形区域;但如遇拥塞或时序需求,可临时越界。 - 自定义属性

REGIONORDER、PURPOSE便于后端脚本按优先级和用途批量处理这些区域。

2.19 Rows

语法

ROW <rowName> <siteName> <origX> <origY> <siteOrient>

[ DO <numX> BY <numY> [ STEP <stepX> <stepY> ] ]

[ + PROPERTY { <propName> <propVal> } … ]

; 功能解释ROW 语句定义版图中的placement site 行(row),由重复排列的 LEF SITE 单元构成,并可为行附加自定义属性。它是标准单元/ASIC 流程中floorplan的核心部分,决定了宏或标准单元可摆放的位置与方向。citeturn8file2turn8file3

参数详解

| 参数 | 类型 / 范围 | 默认 | 说明 |

|---|---|---|---|

<rowName> | 字符串 | — | 行的唯一标识符,用于后续引用(如 + ROUTEHALO 中指定 block 划分时)。 |

<siteName> | 字符串 | — | 在 LEF 中定义的 SITE 名称,指定每个格点的几何模板(如 “core_site”)。 |

<origX> <origY> | 整数 | — | 第一(左下)格点的坐标(DEF 数据库单位,通常对应微米×1000)。 |

<siteOrient> | 枚举:N/S/E/W/FN/FS/FE/FW | N | 行方向:– N:正向;– FN:翻转后;– 其余参见“指定方向” citeturn8file2。 |

DO <numX> BY <numY> | 两个正整数 | 等同 DO 1 BY 1 | 在 X、Y 方向分别重复放置 <numX>、<numY> 个相同 site;其中一者必须为 1(横行或竖列)。 |

STEP <stepX> <stepY> | 两个整数 | 由 LEF SITE 定义的 pitch | 相邻 site 之间在 X、Y 方向上的间距。若省略,则使用 SITE 自带的 X/Y pitch。 |

+ PROPERTY {…} | 键 值 对 列 表 | — | 对此行附加在 PROPERTYDEFINITIONS 中声明的自定义属性,用于脚本、布局约束或后端标记。 |

示例

# 假设 LEF 中已定义 SITE core_site 尺寸 0.8μm×2.0μm

ROWS 5 ;

# 1. 默认行:单 site,原点 (0,0),方向 N

ROW row_0 core_site 0 0 N ;

# 2. 重复 10 列(横向),间距取 site pitch(0.8μm)

ROW row_1 core_site 0 2000 N DO 10 BY 1 ;

# 3. 自定义 X 间距为 1000 dbu (1.0μm)

ROW row_2 core_site 0 4000 N DO 5 BY 1 STEP 1000 0 ;

# 4. 添加脚本可识别的属性

ROW row_3 core_site 0 6000 N

+ PROPERTY ROWORDER 1

+ PROPERTY REGION "CORE_AREA"

;

END ROWS- row_0:单行单点,最简单格式。

- row_1:生成 10 个并排 site,可快速铺满 core 区域。

- row_2:与前者等效,但 X 方向步长显式设为 1.0 μm。

- row_3:在 row_2 基础上,附加自定义属性

ROWORDER和REGION,支持后端工具按优先级与区域划分处理。

2.20 Scan Chains

语法

SCANCHAINS <numScanChains> ;

– <chainName>

[ + PARTITION <partitionName> [ MAXBITS <maxBits> ] ]

[ + COMMONSCANPINS [ ( IN <inPin> ) ] [ ( OUT <outPin> ) ] ]

+ START { <fixedInComp> | PIN } [ <outPin> ]

[ + FLOATING

{ <floatingComp>

[ ( IN <inPin> ) ]

[ ( OUT <outPin> ) ]

[ ( BITS <numBits> ) ]

} …

]

[ + ORDERED

{ <fixedComp>

[ ( IN <inPin> ) ]

[ ( OUT <outPin> ) ]

[ ( BITS <numBits> ) ]

} …

]

+ STOP { <fixedOutComp> | PIN } [ <inPin> ]

;

…

END SCANCHAINS 功能解释

SCANCHAINS 段用于在 DEF 文件中定义扫描链(scan chains),即将若干包含扫描输入(SI)和扫描输出(SO)引脚的触发器或单元按照特定顺序或分组组织成链,以供 DFT(Design-for-Test)工具在后端做扫描测试向量的加载与回取。各项参数提供链的分区管理、公共和个别端口指定、起点/终点、及可调顺序等灵活配置。

参数详解

| 参数 | 类型 / 取值 | 默认 | 说明 |

|---|---|---|---|

<numScanChains> | 正整数 | — | 扫描链的总数,应与后续 – 条目数一致。 |

<chainName> | 字符串 | — | 扫描链标识符,每条 – <chainName> 描述一个链。 |

+ PARTITION <name> | 字符串 + [ MAXBITS 整数 ] | 各链单独分区 | 将链归入同一 <name> 分区,允许在该组内重新分配或交换元素。MAXBITS 限定本链在该分区内最多含的触发器总位数(mismatch 报错或截断)。 citeturn9file9 |

+ COMMONSCANPINS (IN…)(OUT…) | 可选公共 SI/SO 引脚对 | — | 对于未在后续 FLOATING/ORDERED 中单独指定端口的单元,使用此公共 SI、SO。至少需定义公共引脚或在各元素上显式给定。 |

| `+ START { | PIN} []` | 起点,组件或顶级 I/O | — |

+ FLOATING {…} | “浮动”列表,0 或 1 个 | — | “可重排序”元素集合:– <floatingComp>: 组件名;– (IN pin)/(OUT pin): 各自端口;– (BITS n): 本组件位宽(flip‑flop 数),默认 1。– 较少顺序限制,可跨链交换(同分区内)。 |

+ ORDERED {…} | “有序”列表,可多个 | — | “固定顺序”元素集合,与 FLOATING 类似,但顺序不可变;至少需列出两项,链综合时按此列表顺序合成。 |

| `+ STOP { | PIN} []` | 终点,组件或顶级 I/O | — |

示例

SCANCHAINS 1 ;

- SC1

+ PARTITION clk_group MAXBITS 1024

+ COMMONSCANPINS ( IN SI_ALL ) ( OUT SO_ALL )

+ START SIN_PAD OUT

+ FLOATING C1 ( IN D ) ( OUT Q )

C2 ( IN D ) ( OUT Q )

C3 ( IN D ) ( OUT Q ) ( BITS 4 )

+ ORDERED U1 ( IN SI ) ( OUT SO )

U2 ( IN D ) ( OUT Q ) ( BITS 2 )

+ STOP SOUT_PAD IN

;

END SCANCHAINS- 链名:

SC1,仅一条扫描链。 - 分区:隶属

clk_group,最大位数 1024。 - 公共端口:默认

SI_ALL/SO_ALL,若子单元无个别端口则使用。 - 起点:顶级 I/O

PIN SIN_PAD的 OUT 端口。 - 浮动元素:

C1–C3,其中C3是 4 位寄存器,余两者各 1 位,可在分区内任意排序。 - 有序元素:

U1、U2,其中U2为 2 位宽,合成工具须按此顺序排列。 - 终点:

PIN SOUT_PAD的 IN 端口。

2.21 Slots

语法

SLOTS <numSlots> ;

– LAYER <layerName>

{

RECT (<x1> <y1>) (<x2> <y2>)

| POLYGON (<x1> <y1>) (<x2> <y2>) (<x3> <y3>) …

} …

; …

END SLOTS 功能解释SLOTS 段定义在各 routing 或其他层上切孔(slot)的几何区域,用于告诉后端工具哪些区域不应排布完整的金属线,以实现如电网分段、电流泄放或局部连通性需求。

<numSlots>指定本段落包含的– LAYER条目数,而非所有矩形/多边形的总数;- 每个

LAYER条目可列出多个RECT或POLYGON形状,分别定义若干矩形或多边形 slot; - 矩形 slot 用

RECT给出左下、右上两点;多边形 slot 用POLYGON给出 ≥3 顶点,边可平行 X/Y 轴或 45° 斜向; - 工具在布线路径生成时避开这些 slot 区域。 citeturn10file0

参数详解

| 参数 | 类型 | 单位 | 默认 / 取值 | 说明 |

|---|---|---|---|---|

<numSlots> | 正整数 | — | — | 后续 – LAYER 条目数(每层一个),与段内矩形/多边形总数无关。 |

<layerName> | 字符串 | — | — | 指定 slot 生效的层名,一般为 routing 层(如 MET1、M2),或 masterslice、implant 等非路由层。 |

RECT (x1 y1) (x2 y2) | 坐标对 | DEF 单位(如 dbu) | x2>x1, y2>y1 | 定义一个矩形 slot:左下角 (x1,y1)、右上角 (x2,y2)。 |

POLYGON (x1 y1)… | 坐标序列 | DEF 单位 | ≥3 点 | 定义一个多边形 slot:至少 3 个点,按顺序连边并闭合。要求所有边平行 X/Y 轴或 45° 斜角。可用 * 重复上一个点的同一坐标分量。 citeturn10file2 |

示例

1. 多层矩形 Slots

SLOTS 2 ;

– LAYER MET1

RECT ( 1000 2000 ) ( 1500 4000 )

RECT ( 2000 2000 ) ( 2500 4000 )

RECT ( 3000 2000 ) ( 3500 4000 ) ;

– LAYER MET2

RECT ( 1000 2000 ) ( 1500 4000 )

RECT ( 1000 4500 ) ( 1500 6500 )

RECT ( 1000 7000 ) ( 1500 9000 )

RECT ( 1000 9500 ) ( 1500 11500 ) ;

END SLOTS该段为 MET1 和 MET2 两层各定义了三个和四个矩形 slot,后端布线时会在这些区域跳过常规 metal 走线。

2. 矩形 + 多边形混合

SLOTS 1 ;

– LAYER metal1

RECT ( 100 200 ) ( 150 400 )

POLYGON ( 100 100 ) ( 200 200 ) ( 300 200 ) ( 300 100 )

RECT ( 300 200 ) ( 350 400 ) ;

END SLOTS在 metal1 上定义两个矩形和一个 L 形多边形 slot,演示 POLYGON 如何支持非矩形切孔。

2.22 Special Nets

语法

SPECIALNETS <numNets> ;

– <netName>

[ ( {<compName> <pinName> | PIN <pinName>} [+ SYNTHESIZED] ) ] …

[ + VOLTAGE <volts> ]

[ <specialWiring> … ]

[ + SOURCE {DIST | NETLIST | TIMING | USER} ]

[ + FIXEDBUMP ]

[ + ORIGINAL <oldNetName> ]

[ + USE {ANALOG | CLOCK | GROUND | POWER | RESET | SCAN | SIGNAL | TIEOFF} ]

[ + PATTERN {BALANCED | STEINER | TRUNK | WIREDLOGIC} ]

[ + ESTCAP <wireCapacitance> ]

[ + WEIGHT <weight> ]

[ + PROPERTY {<propName> <propVal>} … ]

;

…

END SPECIALNETS功能解释

SPECIALNETS 段用于定义特殊网络,其连接和布线往往由专用“special router”或手工完成,而后续的普通信号路由器不应再修改:

- 常见用途:电源网格 (

POWER)、时钟 mesh、flip‑chip bump 互连、高速或模拟关键走线、DRCFILL 区域等; - 网络成员:可混合实例引脚与顶层

PIN,并标记为SYNTHESIZED; - 电压标注:用

+ VOLTAGE为电源或 I/O 网附上电压值; - 专用布线:通过一系列

specialWiring(如+ ROUTED、+ SHAPE DRCFILL、+ VIA)精确指定走线或填充形状; - 约束与属性:可设置

+ FIXEDBUMP、+ USE、+ PATTERN、+ ESTCAP、+ WEIGHT及自定义+ PROPERTY,指导后端工具在时序、SI、功耗和 DRC 校验时区别对待。 citeturn10file3turn10file5

参数详解

| 参数 | 类型 / 取值范围 | 默认 | 说明 |

|---|---|---|---|

<netName> | 字符串 | — | 特殊网络名称,用于后续引用。 |

( … ) 列表 | 列表:<compName> <pinName> 或 PIN <pinName> | — | 网络连接点:实例引脚或顶级 PIN。+ SYNTHESIZED 标记自动插入的扫描或序列引脚。 |

+ VOLTAGE <volts> | 浮点数 或 整数 | — | 电源网电压(V),供电网或 I/O pad 验证、功耗/EM 分析使用。 |

<specialWiring> | 一组关键字组合:+ ROUTED/+ VIA/+ SHAPE… | — | 精确布线或填充指令,例如:+ ROUTED metal1 (0 0) (1000 0)+ SHAPE DRCFILL |

+ SOURCE {…} | 枚举:DIST/NETLIST/TIMING/USER | NETLIST | 数据来源类型,影响工具决策或日志归属。 |

+ FIXEDBUMP | 关键字 | 否 | 标记 bump net,防止自动工具重定向至其它 pad 或 pin。 |

+ ORIGINAL <oldNetName> | 字符串 | — | 指示本网络源自旧网 <oldNetName>,便于结果回溯和版本对比。 |

+ USE {…} | 枚举:ANALOG/CLOCK/GROUND/POWER/… | SIGNAL | 网络用途分类,用于路由器和电磁分析区分对待。 |

+ PATTERN {…} | 枚举:BALANCED/STEINER/TRUNK/WIREDLOGIC | — | 布线拓扑偏好,如时钟树 STEINER、主干+分支 TRUNK。 |

+ ESTCAP <wireCapacitance> | 浮点数 | — | 估算电容(pF 或 DEF 单位),辅助时序或信号完整性验证。 |

+ WEIGHT <weight> | 整数 或 浮点数 | 1 | 优先级权重,数值越大工具分配资源越多。 |

+ PROPERTY {…} | 一组键值对 | — | 自定义属性,必须先在 PROPERTYDEFINITIONS 中声明,用于 DFT、DFP 或后端脚本集成。 |

示例

SPECIALNETS 1 ;

- VDD_MESH

( U1 VDD ) ( U2 VDD ) ( PIN VDD_PAD )

+ VOLTAGE 1.2

+ USE POWER

+ FIXEDBUMP

+ PATTERN TRUNK

+ ESTCAP 0.05

+ WEIGHT 10

+ ROUTED metal2 ( 0 0 ) ( 1000 0 ) ( 1000 500 )

+ VIA via12 ( 1000 500 )

+ SHAPE DRCFILL

+ PROPERTY DOMAIN "POWER" ;

END SPECIALNETS- 定义单条特殊电源网

VDD_MESH,连接两实例和一个顶级 pad。 - 标注电压、用途和 bump 固定;指定主干布线、via 位置及 DRCFILL 形状;附加自定义属性

DOMAIN="POWER"。 Through this, a special router will generate and preserve this power mesh exactly as specified.

2.23 Styles

语法

STYLES <numStyles> ;

– STYLE <styleNum> <pt1> <pt2> … <ptN> ;

…

END STYLES

<numStyles>:本节中定义的STYLE条目数。STYLE <styleNum>:整数编号(≥0),首个须为 0,后续递增,用于在后续ROUTED/NEW…+ STYLE中引用。<pti>:点坐标对(x y),至少两个,最多八个;可用*重复上一个坐标分量。

功能解释

Styles 定义每条线段端点的凸多边形外轮廓,用于精确控制线段宽度和端帽形状。工具将中心线(或 via)两端各加半个样式多边形,得到完整的线段几何。常用八边形(octagon)或方形(square)样式,也可用 2~8 点定义任意凸多边形。

参数详解

| 参数 | 类型 / 取值范围 | 默认 | 说明 |

|---|---|---|---|

<numStyles> | 正整数 | — | 本节中包含的 STYLE 定义条目数。 |

styleNum | 整数(≥0),首个为 0,后续按需连续递增 | — | 本文件内局部键值,用于后续路由语句中引用该 STYLE。不跨文件保留。 |

pt (x y) | 两个整数坐标(DEF 单位)或 ( * y ) / ( x * ) 重复前一坐标分量 | — | 多边形顶点列表,至少 2 点,最多 8 点;顺序连线后闭合。· 凸性:顶点必须构成凸多边形;· 边方向:必须平行 X 轴、Y 轴或 ±45°。· 中心包含:多边形须包含 (0 0)。 |

示例

STYLES 1 ;

– STYLE 1

( 30 10 ) ( 10 30 ) ( -10 30 ) ( -30 10 )

( -30 -10 ) ( -10 -30 ) ( 10 -30 ) ( 30 -10 ) ;

END STYLES以上定义一个八边形样式,端点凸出的角度与常见 octagon 相同,用于在路由命令中指定。

2.24 Technology

语法

[TECHNOLOGY technologyName ;]功能解释

该语句用于在 DEF 文件中指定当前设计所使用的工艺名称,并将其记录到数据库中。如果多次出现 TECHNOLOGY 语句且名称不一致,后续的名称不会覆盖已生效的名称,数据库中依旧保留先前已定义的工艺名称。

参数说明

| 参数名 | 含义 | 取值类型 | 备注 |

|---|---|---|---|

| technologyName | 工艺名称(标识符) | 字符串(不区分大小写) | 定义设计所用工艺的名称,可任意命名,但应与工具链或数据库中已有工艺名称保持一致。 |

示例

DESIGN myDesign ;

TECHNOLOGY tsmc_28nm ;

UNITS DISTANCE MICRONS 1000 ;

...

END DESIGN

在上述示例中,将工艺名称设置为 tsmc_28nm,后续工具在解析 DEF 时会将此工艺名称与内部工艺库做关联。

2.25 Tracks

语法

TRACKS

{

{X | Y} <start> DO <numTracks> STEP <space>

[ MASK <maskNum> [ SAMEMASK ] ]

[ LAYER <layerName> … ]

;

} … 功能解释TRACKS 用于在 DEF 中定义标准单元设计的路由参考线(routing tracks),包括横向(Y)或纵向(X)方向上的起点、条数、间距,以及多重图案化掩膜、图层约束等信息。通常由 floorplan 初始化时自动生成,以 LEF 中各层的 OFFSET 和 PITCH 为基础。

参数详解

| 参数 | 类型 | 单位 | 默认 / 取值 | 说明 |

|---|---|---|---|---|

X | Y | 关键字 | — | — | 指定方向:– X:竖直(竖线)参考轨;– Y:水平(横线)参考轨。 |

<start> | 整数 / 浮点数 | DEF 单位 | 第一个轨道坐标 | 第一条参考线的全局坐标位置(绝对值),通常与 LEF 层 OFFSET 对齐。 |

DO <numTracks> | 整数 ≥1 | — | — | 要创建的参考线数量。不能为 0。 |

STEP <space> | 整数 / 浮点数 | DEF 单位 | LEF 层 PITCH | 相邻两条参考线之间的间距。若省略,使用 LEF 中对应层的 PITCH。 |

MASK <maskNum> | 整数 | — | 交替循环(默认) | 指定多重图案化工艺的起始掩膜编号(通常为 1/2/3);若无此项,则所有轨道“无色”。 |

SAMEMASK | 关键字 | — | 循环(默认) | 如果加上此关键字,则所有轨道均使用同一个 maskNum,而不是按 1,2,1,2… 或 1,2,3,1… 循环。 |

LAYER <layerName> … | 字符串列表 | — | 所有 routing 层 | 指定哪些 LEF 定义的 routing 层适用本条轨道。如列多层,则同一组轨道同时用于这些层。可省略,仅定义掩膜时不指定图层。 |

示例

# 在 metal1 上定义 100 条竖直轨道:

TRACKS

X 0 DO 100 STEP 200 MASK 1 SAMEMASK LAYER metal1

;

# 在 metal2 和 metal3 上定义 50 条水平轨道,起点 Y=100,间距 300:

TRACKS

Y 100 DO 50 STEP 300 LAYER metal2 metal3

;

END TRACKS- 第一条:从 X=0 开始,生成 100 条竖线,每条间隔 200 unit,全都使用 mask 1,并仅在

metal1层可路由。 - 第二条:从 Y=100 开始,生成 50 条横线,每条间隔 300 unit,同时应用于

metal2和metal3两层,使用默认循环掩膜(如果是多掩膜层则交替 1,2,1…)。

2.26 Units

语法

UNITS DISTANCE MICRONS <dbuPerMicron> ;功能解释

UNITS 段用于设置 DEF 文件中所有坐标、尺寸的单位比例因子,即定义1 微米(μm)对应多少 DEF 单位(dbu)。这保证了后续如引脚坐标、行、宏位置、间距、金属宽度等字段的单位一致性。通常配合 LEF 文件中的 UNITS DATABASE MICRONS 一致设定。

dbu(Database Units):一种内部整数单位,所有 DEF 文件坐标都以此单位表达。

参数详解

| 参数 | 类型 | 示例值 | 说明 |

|---|---|---|---|

DISTANCE | 关键字 | — | 固定写法,表示设置距离单位比例。 |

MICRONS | 关键字 | — | 固定写法,表示 1 微米为基本物理单位。 |

<dbuPerMicron> | 正整数 | 1000 | 表示 1 微米 = dbuPerMicron DEF 单位,常见值:100、1000、2000、10000。推荐使用1000(即 0.001 μm 分辨率) |

示例

UNITS DISTANCE MICRONS 1000 ;- 表示后续所有尺寸、坐标都以1 微米 = 1000 DEF 单位为基准。

- 如元件位置

(15000, 3000)实际为(15 μm, 3 μm)。 - 例如行 pitch 设置为

STEP 800 0,表示行高为0.8 μm。

注意事项:

- 本字段通常必须放在

DESIGN声明之后、所有坐标相关语句之前; - 若 DEF 与 LEF 所用单位不一致,可能导致布局偏移或比例失配;

- 工具读取时会根据

dbuPerMicron自动换算为实际 μm。

2.27 Version

语法

VERSION <versionNumber> ; 注:整个语句以分号结束,与其他 DEF 语句格式一致。

功能解释

VERSION 语句声明本 DEF 文件所使用的 DEF 语言版本,格式为“主版本号.次版本号[.子次版本号]”(例如 5.8、5.8.1)。虽然此语句在 DEF 中非必需,但强烈建议显式指定,以避免:

- 语法不兼容:新版本语法扩展在旧工具中被视为错误;

- 工具默认差异:不同版本的路由/验证工具默认支持的 DEF 版本不同,显式声明可确保一致解析。 citeturn15file4citeturn15file7

参数详解

| 参数 | 类型 | 取值格式 | 默认 | 说明 |

|---|---|---|---|---|

<versionNumber> | 字符串 | major.minor[.subMinor] | 无(未声明) | DEF 语法版本号:– major:主版本号(整数);– minor:次版本号(整数);– subMinor:可选子次版本(整数)。 |

示例

VERSION 5.8 ;在上述示例中,DEF 解析器和后端工具会以 5.8 版本的 DEF 语法规则读取此文件,确保对 5.8 中新增或修改的语句(如 TRACKS、STYLES、SLOTS 等)正确支持。若该语句缺失,部分工具可能默认使用其自身的最高支持版本,存在不确定性。

2.28 Vias

语法

VIAS <numVias> ;

– <viaName>

[

+ VIARULE <viaRuleName>

+ CUTSIZE <xSize> <ySize>

+ LAYERS <botMetalLayer> <cutLayer> <topMetalLayer>

+ CUTSPACING <xCutSpacing> <yCutSpacing>

+ ENCLOSURE <xBotEnc> <yBotEnc> <xTopEnc> <yTopEnc>

[ + ROWCOL <numCutRows> <numCutCols> ]

[ + ORIGIN <xOffset> <yOffset> ]

[ + OFFSET <xBotOffset> <yBotOffset> <xTopOffset> <yTopOffset> ]

[ + PATTERN <cutPattern> ]

]

|

[

+ RECT <layerName> [ MASK <maskNum> ] <x1> <y1> <x2> <y2>

| + POLYGON <layerName> [ MASK <maskNum> ] <x1> <y1> <x2> <y2> <x3> …

] …

; …

END VIAS 功能解释

VIAS 段定义设计中所有 via(穿孔) 的类型与几何形状。它支持两种方式:

- Generated Via(自动 via)——使用

+ VIARULE及一系列参数由路由器自动生成 via; - Fixed Via(固定 via)——使用

+ RECT或+ POLYGON明确定义每层形状。

所有 via 均包含三层几何:底层金属 → 切层 → 顶层金属。该段既可用于宏内局部 via,也可用于全设计 via 列表。

参数详解

| 参数 | 类型 / 范围 | 默认 | 含义 |

|---|---|---|---|

<numVias> | 正整数 | — | VIAS 条目数,应等于后续 – <viaName> 行数。 |

<viaName> | 字符串 | — | via 的标识符,可在 COMPONENT、PINS、SPECIALNETS 等节中引用。 |

+ VIARULE <rule> | 字符串 | 无 / 继承 LEF | 指定 LEF 中的 VIARULE GENERATE 规则名,用以自动生成 via。 |

+ CUTSIZE <x> <y> | 浮点或整数(dbu) | LEF 定义 | 切层(cut)在 X、Y 方向上的尺寸。 |

+ LAYERS <bot> <cut> <top> | 字符串 × 3 | — | 指定 via 的三层:底层金属层名、切层名、顶层金属层名。 |

+ CUTSPACING <x> <y> | 浮点或整数(dbu) | LEF 定义 | 切孔间的最小边缘间距,X 与 Y 可不同。 |

+ ENCLOSURE <bX> <bY> <tX> <tY> | 浮点或整数(dbu) | LEF 定义 | 决定金属层相对于 via 切孔的最小扩展量:– <bX>,<bY>:底层金属;– <tX>,<tY>:顶层金属。 |

+ ROWCOL <r> <c> | 正整数 | 1×1 | 指定切孔阵列的行数 (r) 与列数 (c);仅在 VIARULE 生成 via 时有效。 |

+ ORIGIN <x> <y> | 浮点或整数(dbu) | via 中心 | via 原点坐标(相对于实例原点),覆盖 LEF 原始对齐。 |

+ OFFSET <bX> <bY> <tX> <tY> | 浮点或整数(dbu) | LEF 定义 | 额外的底层/顶层金属偏移,用于微调 via 与金属的包覆关系。 |

+ PATTERN <pattern> | 字符串 | 无 | 指定 via 切层的图案(如多重图案化时采用的交错样式)。 |

+ RECT <layer> [MASK m] <x1> <y1> <x2> <y2> | 坐标对,dbu | — | 在 <layer> 上绘制矩形 via 形状:– MASK m: 可选的多重图案化掩膜编号;– <x1,y1>:左下;<x2,y2>:右上。 |

+ POLYGON <layer> [MASK m] <x1> <y1> … | 坐标列表,dbu | — | 在 <layer> 上绘制多边形形状,至少 3 点,按顺序连接并闭合,多边形须凸且边平行 X/Y 或 45°。 |

示例

1. 自动via

VIAS 1 ;

– auto_via

+ VIARULE via_12_gen

+ CUTSIZE 50 50

+ LAYERS metal1 via12 metal2

+ CUTSPACING 60 60

+ ENCLOSURE 20 20 30 30

+ ROWCOL 2 2

+ ORIGIN 100 200

+ OFFSET 5 5 5 5

+ PATTERN checker

;

END VIAS2.固定via

VIAS 1 ;

– fixed_via

+ RECT metal1 MASK 1 (0 0) (100 200)

+ RECT via12 (25 50) (75 150)

+ RECT metal2 MASK 2 (0 0) (100 200)

;

END VIAS- auto_via 使用

via_12_gen规则自动生成 2×2 切孔阵列,底层/顶层金属扩展及偏移微调; - fixed_via 明确定义三层矩形形状,底层/顶层带不同

MASK,中间切层无色。

3. 参考

【1】lefdefref.pdf

4. 获取参考文档

关注【蓝色天空】博客的公众号,并在公众号里发送对应的下载关键字【KX002】获取下载链接。