本文始于2025年6/7月,浅谈应力迁移(SM)失效机制,旨在让读者基本了解 SM 是什么,对设计有哪些影响,以及介绍减少SM的一些方法。

1. 什么是应力迁移(SM)?

SM,全称:Stress Migration,是指:金属互连在制造或封装后因应力集中(如热膨胀系数不匹配)而发生原子迁移、局部空洞或裂纹,最终导致导电路径断裂或电阻异常升高的现象。

是一种发生在集成电路 金属互连层(通常为铝或铜)中,由于热应力或机械应力引发原子迁移和空洞形成的可靠性失效机制。它在现代 VLSI—Very Large Scale Integration 后端工艺(特别是高密度互连和多金属层)中是一种典型的失效问题。

2. 发生原因与物理机制

🔸 2.1 热膨胀不匹配(CTE mismatch)

- 铜的热膨胀系数(~17 ppm/°C)远高于低k介质或 SiO₂(~0.5 ppm/°C)。

- 在反复的温度变化(如工艺退火、芯片通断电、环境温度变化)中, 铜会“伸缩”更多,导致与周围介质之间产生强烈机械应力。

🔸 2.2 金属内应力释放(Stress relaxation)

铜在沉积和冷却过程中就产生“内建应力”;随时间推移,铜原子为了“减压”,在应力驱动下,金属原子会从高应力区迁移到低应力区,可能自发地迁移(尤其是在晶界、界面处)。导致高应力区域 原子空位累积,最综空洞形成。

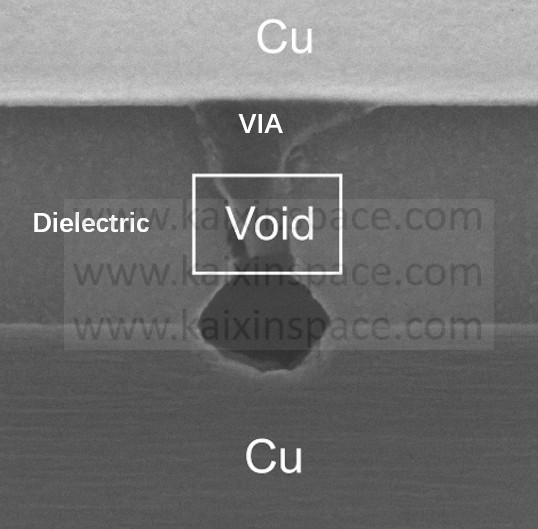

🔸 2.3 界面弱的结合处易形成“空洞”

VIA底部或金属层突变点是应力集中处,极易形成空洞(Voiding Nucleation Sites),一旦空洞扩展,电阻将升高,热效应增加,最终导致器件开路失效。

特别在 高温烘烤、冷热冲击、封装应力测试后 这些地方更容易出现空洞。

参考如下图片:

3. 减少SM的一些方法

3.1 设计方面

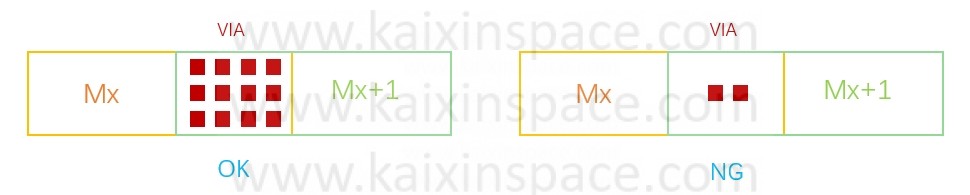

- 选择合适的VIA数量与过孔结构:遵守工艺文档相关SM规则:如 VIAx.R.2~R.11等等(更多规则见工艺手册),规则中规定每种宽度金属最少要几个 VIA;增加 VIA 数量、缩小间距,降低单个 VIA 承受的应力集中度。

- 避免大面积金属块孤立连接:例如,一个较大的金属块只通过一两个 VIA 接地,很容易在热循环中“拉断”;尽量布多个等距 VIA、使用 Mesh 结构。

- 使用对称VIA 分布:在一些关键匹配电路中,使用对称布局可以均衡应力分布,减少单点故障;

💡 如条件容许,应进行热应力仿真,识别应力集中点,并通过 DFM 改善设计。

3.2 工艺方面

- 铜沉积工艺优化:使用 低应力镀铜技术;控制镀铜电流密度和时间,减少初始应力堆积;应用双镀铜(dual damascene)结构,提高应力分布均匀性。

- 退火(Annealing)工艺控制:控制退火条件,采用多阶段或渐进式退火,缓慢释放铜内建应力,防止热应力突变。

- 选用低应力材料:低内应力的Cu,合适的CTE介电材料,另外别忘记封装材料的选用,也要注意,因为封装材料的热和机械兼容性直接影响应力迁移强度。

4. 与电迁移(EM)的对比

| 特性 | 应力迁移(SM) | 电迁移(EM) |

|---|---|---|

| 驱动力 | 机械/热应力(不需要电流) | 电流密度 + 电场(需要电流) |

| 时间点 | 通常在制造后早期失效 | 长期工作中逐渐老化 |

| 常见位置 | VIA区, 应力集中处,封装边缘 | 金属线弯折、窄线、热点区域 |

| 典型场景 | 热循环、退火、封装应力 | 大电流、高温操作 |

5. 参考

【1】tsmc specification document