本文始于2025年6/7月,浅谈 Low-k Dielectric Integrity 失效机制,旨在让读者基本了解 Low-k Dielectric Integrity 是什么,有哪些影响,以及介绍减少Low-k Dielectric 失效的一些措施。

1. 什么是 Low-k Dielectric Integrity?

Low-k Dielectric Integrity 指的是低介电常数(Low-k)材料在长期电应力、热应力下的绝缘能力和可靠性保持能力。如果 Low-k 材料发生击穿,两个金属线之间可能短路,导致芯片功能失效。发生在金属互连层。

⭐ 使用 Low-k 材料的优缺点:

优点:传统 SiO₂ 的介电常数约为 4;而Low-k 材料(如 SiOC、SiLK)介电常数可低至 2.5~3;这样可以有效降低互连线间电容从而提高速度和降低功耗。

缺点:Low-k材料更容易吸水、起泡、形成空洞,并且更容易发生 时间依赖性电介质击穿(IMD-TDDB)。

💡 IMD-TDDB:Inter-Metal Dielectric Time-Dependent Dielectric Breakdown,金属间介质时间依赖性介电击穿。

2. 失效机制(Failure Mechanisms)

导致 Low-k 材料击穿的两种机制:

1️⃣ 介电界面击穿,Dielectric Interface Breakdown :由于Low-k 材料孔隙率高、Cu 离子残留、ESL(etch stop layer)整合不良等原因;导致原子迁移或杂质堆积造成界面弱化。

2️⃣ 介电体本体击穿,Dielectric Bulk Breakdown :材料本体存在空洞(Porosity)和 缺陷路径(如 Trench barrier formation),电流会沿这些路径“钻通”整层 Low-k 材料。

📌 最终的结果就是:金属线之间形成泄漏通道,导致芯片失效。

3. 寿命预测模型(Lifetime Model)

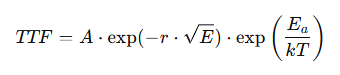

常见的模型如下:

| 项目 | 含义 |

|---|---|

| TTF | Time To Failure(失效时间) |

| A | 经验常数 |

| r | 电场加速因子 |

| E | 电场强度(MV/cm) |

| Ea | 激活能(eV) |

| k | Boltzmann 常数(8.617×10⁻⁵ eV/K) |

| T | 温度(K) |

📌 从模型可以看到:电场越高(E 越大),TTF 越低(寿命越短);温度越高,击穿越容易发生。

4. 减少 Low-k Dielectric 失效的一些措施

- 增大金属线间距,降低单位面积电场;

- 使用宽线+多 VIA 组合减小局部热量堆积;

- 采用机械强度更高的 low-k 材料;

5. 参考

【1】tsmc specification document