本文始于2025年6/7月,浅谈负偏置温度不稳定性(NBTI)的失效机制,旨在让读者基本了解 NBTI 是什么,对设计有哪些影响,以及介绍一些降低NBTI效应的预防措施。

1. 什么是负偏置温度不稳定性(NBTI)?

NBTI,全称:Negative Bias Temperature Instability,负偏置温度不稳定性,是一种主要发生在 PMOS 晶体管中的老化失效机制,在 负栅偏压(Gate Bias < 0) 和 高温 条件下加速发生。对于电路设计者而言,有必要考虑其设计的寿命衰减,并且在老化测试、现场运行以及应对工艺偏差的过驱动应用中都必须加以考虑。

📌 NBTI 效应在65nm以下技术节点尤其显著。

2. NBTI 的失效机理

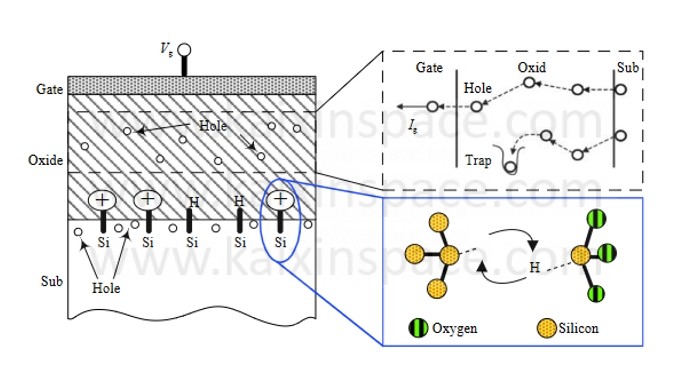

PMOS器件的迁移率低于NMOS器件。在高温环境下,晶体管栅极上的负偏压应力会进一步且显著地降低PMOS器件的迁移率。负偏压下注入到氧化物-衬底界面的空穴会增加界面态。这种电化学反应引发的器件不稳定性会因栅极多晶硅工程工艺中注入的硼而加剧。逻辑电路可能遭受驱动电流下降的影响,而模拟电路则可能面临失配或阈值电压偏移的问题。

恒定电压(DC)下的负偏压温度应力会在栅氧化层与硅衬底之间导致界面陷阱(NIT)的产生,这进而会转化为器件的阈值电压漂移(Vt shift)和饱和电流损耗(Ion loss)。由于PMOS反型层中的空穴已知会与氧化层态发生相互作用,NBTI效应对PMOS的影响比对NMOS更为严重。

NBTI 的失效本质是界面缺陷和正电荷陷阱的形成,总结如下:

- 负栅偏压下,空穴注入氧化层界面:在高温 和 Vg < 0 的应力下,PMOS 中的空穴(从源极流向漏极)被注入至 Si/SiO₂ 界面,引发 界面态(NIT)的生成;这些缺陷是 Si–H 键断裂形成的 dangling bond(悬挂键:化学中指固定原子上未满足的价键)。

- 界面陷阱导致性能退化:陷阱态俘获电荷,使得栅电容调控能力下降;造成 阈值电压 Vt 上升、Ion 降低、PMOS驱动能力减弱。

3. NBTI 的影响

主要表现为:

- 阈值电压(Vt)上升:使 PMOS 打开门槛变高,影响逻辑电路开关时间

- 驱动电流(Idsat)和跨导Gm的减少:驱动能力下降,数字电路速度慢

- 长时间下可能导致模拟电路失配、数字电路速度变慢、逻辑失败

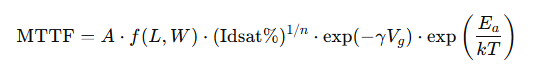

4. NBTI 寿命模型

常见模型用于 NBTI 寿命评估:

参数含义:

| 符号 | 含义 |

|---|---|

| MTTF | Mean Time to Failure(平均失效时间) |

| L, W | 器件的栅长、栅宽(μm) |

| Idsat | 饱和漏电流的下降百分比(如10%) |

| n | 时间相关退化的幂指数 |

| γ | 电压加速因子(负偏压影响) |

| Vg | 栅极工作电压(单位V) |

| Ea | 活化能 |

| k | Boltzmann 常数(8.617×10⁻⁵ eV/K) |

| T | 绝对温度(单位K) |

| A | 常数(与工艺有关)。 |

5. 对比DC和AC情况下寿命模型

1️⃣ AC运行下,由于在 开关切换状态,部分陷阱可自我恢复,当 PMOS 不再施加负压(即恢复为 0V 或浮空)时:

- 部分 Si-H 键可能重新结合;

- 部分陷阱可能“退火”;

2️⃣ DC运行下, 应力退化严重(持续负压);

📌 故此,AC 工作负载下, NBTI 寿命往往较 DC 条件长。

T家采用 AC 与 DC 寿命的换算因子为 2:

- 若 DC 条件下寿命为 5 年,则 AC 条件下可认为为 10 年;

- AC/DC 比例假设设备有 50% 时间处于 off 状态。

6. 一些实验数据分析(来自T家)

💡 注意1:以下测试案例数据,仅提供一些趋势和设计参考;

💡 注意2:对应的数据与工艺和相关测试条件强相关。

有如下相关数据:

| 类型 | PMOS寿命 @Vop | Vop | Vmax | W/L | 温度 |

|---|---|---|---|---|---|

| 1.1V Core (SVT) | 9.88 年 | 1.21V | 1.24V | 10/0.04 | 125°C |

| 1.1V Core (HVT) | 12.7 年 | 1.21V | 1.259V | 10/0.04 | 125°C |

| 1.1V Core (LVT) | 34.7 年 | 1.21V | 1.297V | 10/0.04 | 125°C |

| 1.8V I/O | 6.82 年 | 1.98V | 2.0V | 10/0.15 | 125°C |

| 2.5V OD / 3.3V I/O | 11.5 年 | 2.75V | 3.755V | 10/0.44 | 125°C |

| 2.5V I/O | 374 年 | 2.75V | 3.466V | 10/0.27 | 125°C |

数据分析

1️⃣ LVT PMOS 寿命最佳

- 1.1V Core 中,PMOS 的 NBTI 寿命排名为:LVT > HVT > SVT

- 因为 LVT 的阈值较低 ,实际 Vgs−Vth 较小 ,电场弱 ,所以NBTI 退化慢;同时 Vmax 较高(1.297V)提供更宽裕的操作空间。

2️⃣ Core 电压 PMOS Vmax 容差极小

- 对 SVT 类型,1.21V 操作下 Vmax = 1.24V,只有 30mV 电压余量;

- 说明在 Core 电压区域内,过压非常容易引发 NBTI 失效,需格外控制电源波动。

3️⃣ I/O 工艺器件耐 NBTI能力更强

- 尽管工作在更高电压(如 2.75V),I/O PMOS 的寿命高达 374 年(2.5V I/O);其 Vmax 甚至达到 3.466V;

- 说明 I/O 工艺 PMOS(厚栅氧、长栅长、轻掺杂)在设计上高度加强了可靠性。

4️⃣ 不同器件 W/L 差异对寿命的影响

从上图也可以看出:栅长增加,降低单位电场强度,减轻NBTI退化。

7. 一些预防措施

| 方法 | 说明 |

|---|---|

| 选择高 Vt PMOS | 更高的阈值电压器件在相同栅压下电场较低,NBTI减轻 |

| 适当加长栅长 | 降低栅漏之间的电场强度,降低注入概率 |

| 降低工作电压 | 指数降低 NBTI 速率 |

| 合理时钟占空比设计 | 降低 PMOS 长时间处于开启态的概率 |

| 温度控制 | 降温控制 NBTI |

| 仿真与验证 | 采用 老化模型,对关键路径做 时序老化分析; |

8. 参考

【1】tsmc specification document

【2】深亚微米 p 栅MOSFET中 NBTI效应及氮在其中的作用 — 韩晓亮 郝 跃刘红侠

【3】Model of NBTI combined with mobility degradation — Xuezhong Wu’, Chenyue Ma’, Shucheng Gao’, Xiangbin Lil, Fu Sun’, Lining Zhang. and Xinnan Lin