本文始于2025年6/7月,浅谈热载流子效应(HCI),旨在让读者基本了解 HCI 是什么,对设计有哪些影响,以及介绍一些降低HCI效应的措施。

1. 什么是热载流子注入效应(HCI)?

HCI,全称:Hot Carrier Injection 是指在强电场作用下,MOSFET 中的载流子(电子或空穴)获得高能量,冲破势垒注入到栅氧化层中,从而导致器件性能退化的一种现象。

它是深亚微米MOS工艺中常见的可靠性问题之一,对长期使用的数模混合电路、I/O 驱动器等尤其关键。

2. 物理机制解释

主要有以下几点:

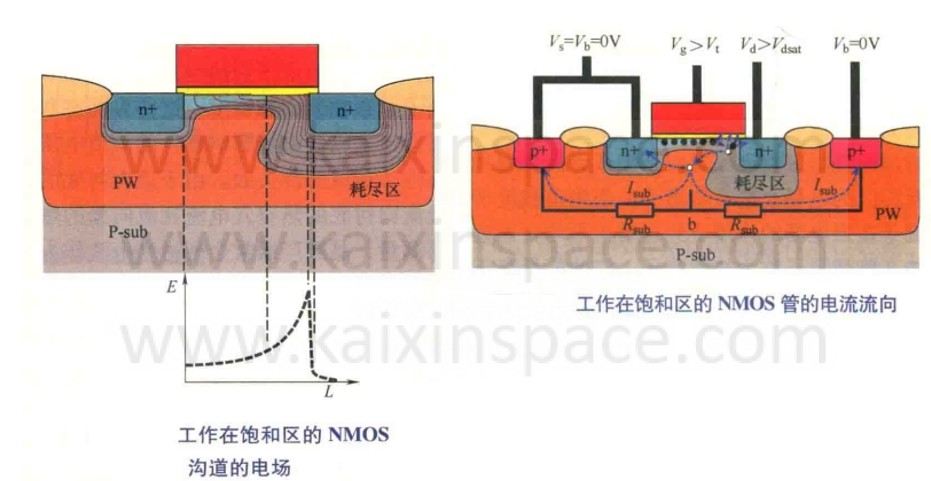

- 载流子加速:在MOS晶体管中,当 漏极–源极电压 Vds 很高 时,沟道中载流子(NMOS 为电子,PMOS 为空穴)会在靠近漏极区域遇到非常强的电场。

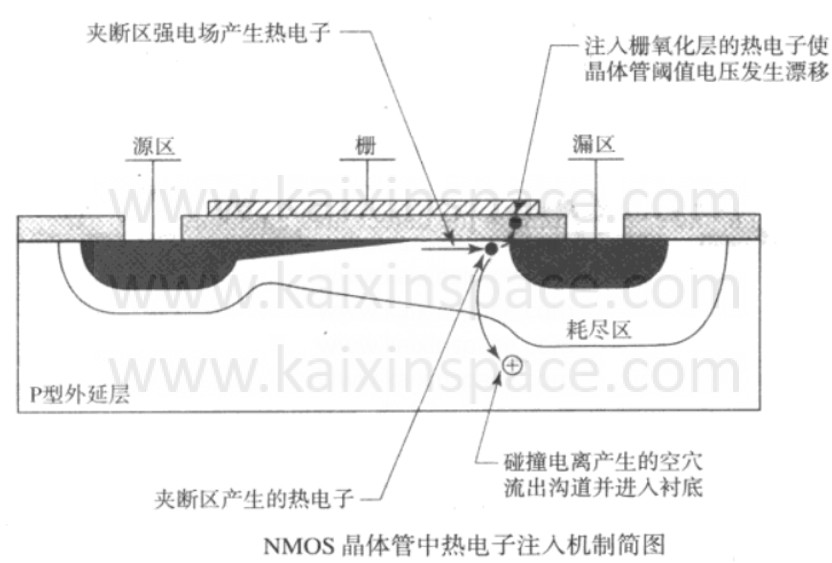

- 能量积累与碰撞:这些载流子被加速,变成“热”载流子,其能量可达几 eV。它们可能撞击 Si 晶格原子,生成电子–空穴对(impact ionization),电子可能穿越氧化层隧穿至栅极或界面,而空穴则沿相反的方向运动,即朝着源区和衬底运动,到达衬底,形成背栅电流。因为空穴对比电子跨越氧-硅界面所需要的能量低,所以背栅电流比栅电流大几个数量级。由于这种背栅电流比起微弱的栅电流更容易测量,所以常用来作为热载流子注入的指标。

- 注入与陷阱形成:高能量载流子会注入到 Si/SiO₂界面 或氧化层内部,形成电荷陷阱或界面态。这些缺陷逐渐积累,导致器件电气特性退化。

📌 与PMOS的区别:PMOS 热载流子效应比 NMOS 弱,主要因为空穴质量大、迁移率低,难以加速到高速,也就不易获得足够能量穿透氧化层。

相关热载流子效应图片如下:

3. 典型失效表现

HCI 主要引起器件以下参数的退化:

| 影响参数 | 后果 |

|---|---|

| 阈值电压 (Vth) 漂移 | 使得MOS开启点变化,影响电路逻辑 |

| 迁移率下降 | 因界面态密度增加,电子受散射增强 |

| 饱和漏电流 (Idsat) 下降 | 导致驱动能力减弱 |

| 串联电阻增加 | 电流路径损耗加剧 |

| 亚阈值特性变差 | 电路噪声边界模糊,尤其影响模拟电路 |

📌 这些变化会造成:

- 电路速度下降;

- 延迟时间增加;

- 器件老化、寿命缩短。

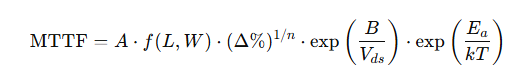

4. 寿命模型(Mean Time To Failure, MTTF)

常见的寿命模型如下:

各参数解释:

| 符号 | 含义 |

|---|---|

| A、B | 经验拟合常数,依赖工艺和测试方式 |

| f(L,W) | 依赖于栅长 L 和宽度 W 的几何函数 |

| Δ% | 失效判据(例如:Idsat 下降10%,或 transconductance Gm 下降10%) |

| n | 失效判据的指数 |

| Vds | 漏源极电压,高Vds加速HCI |

| Ea | 活化能,描述温度影响 |

| k | 玻尔兹曼常数(8.617 × 10⁻⁵ eV/K) |

| T | 绝对温度(单位为 Kelvin)(开尔文 K) |

5. 一些实验数据分析(来自T家)

💡注意1:以下测试案例数据,仅提供一些趋势和设计参考;

💡 注意2:表格中的数据,与工艺和相关测试条件强相关。

5.1 有如下相关数据

| 类型 | 电压等级 | 器件 | W/L | 温度 | MTTF@Vop | Vop | Vmax |

|---|---|---|---|---|---|---|---|

| Core (STD) | 1.1V | NMOS | 10/0.04 | 125°C | 0.211 年 | 1.21V | 1.25V |

| Core (STD) | 1.1V | PMOS | 10/0.04 | 125°C | 0.371 年 | 1.21V | 1.28V |

| 1.8V I/O | 1.8V | NMOS | 10/0.15 | 25°C | 0.285 年 | 1.98V | 2.00V |

| 1.8V I/O | 1.8V | PMOS | 10/0.15 | 25°C | 15.24 年 | 1.98V | 2.251V |

| 2.5V I/O | 2.5V | NMOS | 10/0.27 | 25°C | 1.13 年 | 2.75V | 2.90V |

| 2.5V I/O | 2.5V | PMOS | 10/0.27 | 25°C | 15.1 年 | 2.75V | 3.3V |

| 3.3V I/O | 3.3V | NMOS | 10/0.5 | 25°C | 0.2167 年 | 3.63V | 3.64V |

| 3.3V I/O | 3.3V | PMOS | 10/0.4 | 25°C | 0.39 年 | 3.63V | 3.77V |

5.2 数据分析

1️⃣ Core 电压(1.1V)条件下

- 在1.21V 操作电压时,NMOS 的寿命 仅 0.211 年(≈2.5 个月);

- PMOS 的寿命 0.371 年,稍高但仍远低于设计期望(通常要求 ≥10年);

- 对应的 最大可承受电压(Vmax)仅略高于工作电压(Vop),表明这类器件在核心电压过压条件下非常敏感;

- W/L = 10/0.04,栅长极小,加剧了热载流子效应,寿命大幅缩短。

2️⃣ 1.8V I/O

- NMOS 在 1.98V 下仅有 0.285 年寿命,而 PMOS 有 15.24 年;

- NMOS 的 Vmax 也极接近 Vop(2.0V vs. 1.98V)极易失效;

- PMOS 的裕度相对安全,Vmax 达到 2.251V。

3️⃣ 2.5V I/O

- NMOS 使用寿命提升到 1.13 年;

- PMOS 寿命依旧很好,达 15.1 年;

- 在此电压段中,NMOS 同样对电压变化极其敏感,易失效。

4️⃣ 3.3V I/O:

- NMOS 在 3.63V 电压下寿命仅 0.2167 年(约2.6个月);

- PMOS 寿命为 0.39 年,依然非常短;

- 表明在高电压下,两种器件 均面临极大 HCI 挑战;

- Vmax 相对Vop仅高出一点点,基本无裕量。

5.3 总结

| 要点 | 建议做法 |

|---|---|

| 低栅长 NMOS 寿命短 | 增加栅长(Lg),尤其在高电压 I/O 和 core 中 |

| 温度越高寿命越短 | 保持在合适的工作条件喜下(如,25°C) 更可靠 |

| 高电压下 NMOS 更危险 | IO 接口设计中,NMOS 尽量保守用电压 |

| PMOS 一般更稳定 | 但在极端电压和高温下也会面临可靠性下降 |

| 对 Vmax 要有裕量 | 使用电压应保持在小于Vmax以下更安全 |

6. 降低HCI效应的几种措施

- 减少漏极附近衬底的掺杂浓度,适当加宽夹断区

- 减少漏区外围的掺杂浓度,使耗尽区延伸到漏区(轻掺杂漏区LDD工艺)

- 降低 Vds 使用值:保持在规定工作电压范围内,避免误用 overdrive

- 拉长栅长 L:对关键路径器件可以增加 mos 管 L 值 以降低电场强度

- 降低工作频率或 duty-cycle:减少热载流子作用时间,降低老化速率

- 仿真与布局优化:对 HCI 敏感路径进行 IR-drop、温度分布仿真,避免热点集中

7. 参考

【1】tsmc specification

【2】集成电路制造工艺与工程应用_温德通

【3】The Art of Analog Layout ,Second Edition——Alan Hastings